**Practical tips for the User**

By Steve Roberts M.Sc. B.Sc.

**Technical Director, RECOM**

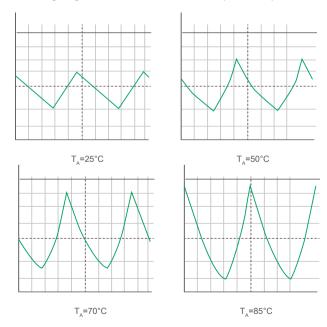

# DC/DC Book of Knowledge Practical tips for the User

Steve Roberts, M.Sc. B.Sc. Technical Director, RECOM

Fifth Edition

© 2021 All rights RECOM Engineering GmbH & Co KG, Austria (hereafter RECOM)

The contents of this book or excerpts thereof may not be reproduced, duplicated or distributed in any form without the written permission of RECOM.

The disclosure of the information contained in this book is correct to the best of the knowledge of the author, but no responsibility can be accepted for any mistakes, omissions or typographical errors. The diagrams illustrate typical applications and are not necessarily complete.

## **Preface from RECOM Management**

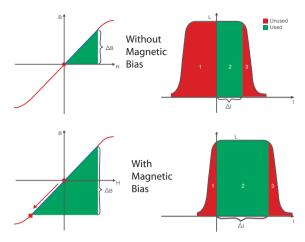

When we introduced our first DC/DC Converter more than 25 years ago, there were little published technical material available and hardly any international standards to follow. There was a pressing need to communicate practical application information to our customers, which prompted us to add some simple Application Notes as an appendix to our first published product catalogue. The content of these guidelines grew over the years as we gained more and more expertise. Although they are still of a rudimentary nature, they are well received by our customer base and today they have become an 70-page Application Note package available for download from our website.

The advance of semiconductor technology and the shift towards highly integrated digital electronics has diminished the knowledge base of analogue techniques in many design labs, universities and technical colleges over the years. We often see a lack of practical know-how in analogue circuit design, particularly with regard to applied techniques, test and measurement and the understanding of filtering and noise suppression. Therefore, as experts in this arena, we saw the need for a much more comprehensive technical handbook that could be used as reference by hardware designers and students alike.

At the start of 2014, Steve Roberts, our Technical Director, started to invest his free time to start documenting the extensive application knowledge on the design, test and application of DC/DC converters available within the RECOM group. Despite all of the pressures of his demanding job, along with new product development and the technical planning of our new research and test labs, he has managed to complete this onerous task in time for Electronica 2014. Today, two years later, in the time for Electronica 2016 the third edition of the RECOM DC/DC Book of Knowledge has been enlarged to include an additional chapter on magnetics.

Steve has presented us with a handbook that we are sure will greatly benefit the engineering community and all those who are interested in DC/DC power conversion and its applications. The handbook will initially be available as a printed version and PDF, not only in English but also in German, Chinese and Japanese.

Board of Directors Gmunden, 2021

**RECOM Group**

## Preface from the Author

The function of any AC/DC or DC/DC converter module is to meet one or more of the following requirements:

- i: to match the secondary load to the primary power supply

- ii: to provide isolation between primary and secondary circuits

- iii: to provide protection against the effects of faults, short circuit or over heating

- iv: to simplify compliance with safety, performance or EMC legislation.

There are a number of different techniques available to achieve these aims, starting at its simplest with a linear regulator and going through to multi-stage, digitally controlled power supplies. This book aims to explain the various DC/DC circuits and topologies available so that users can better understand the advantages, limitations and operational boundaries of each of these solutions. The language used is necessarily technical, but is kept as simple as possible without trivialising the technology involved.

The author has many years of experience answering customers' questions, helping with design-ins, presenting at seminars, writing articles and even making Youtube videos. Despite this accumulated know-how, there is still something to learn new every day about this diverse and wide-ranging subject. This book is subtitled "Practical tips for the User" because it hopes to de-mystify the topic of power conversion, despite there being as many solutions as there are applications. If it succeed in passing at least some of our expertise and knowledge on to you, then it will have accomplished its goal.

The information given in this book is given in good faith and has been checked for veracity, but if the reader finds any errors, omissions and inaccuracies, please feel free to inform me.

Steve Roberts

Technical Director

s.roberts@recom-power.com

Gmunden, 2021

**RECOM**

## **Contents**

| 1.         | Introduction                                 | 1  |

|------------|----------------------------------------------|----|

| 1.1        | Linear Regulators                            | 1  |

| 1.1.1      | Efficiency of a Linear Regulator             | 3  |

| 1.1.2      | Other Properties of the Linear Regulator     | 4  |

| 1.1.3      | LDO Linear Regulators                        | 4  |

| 1.2        | Switching Regulator                          | 6  |

| 1.2.1      | Switching Frequency and Inductor Size        | 7  |

| 1.2.2      | Switching Regulator Topologies               | 7  |

| 1.2.2.1    | Non-Isolated DC/DC Converter                 | 8  |

| 1.2.2.1.1  | Switching Transistors                        | 8  |

| 1.2.2.1.2  | Buck Converter                               | 10 |

| 1.2.2.1.3  | Buck Converter Applications                  | 12 |

| 1.2.2.1.4  | Boost Converter                              | 13 |

| 1.2.2.1.5  | Boost Converter Applications                 | 15 |

| 1.2.2.1.6  | Buck-Boost (Inverting) Converter             | 15 |

| 1.2.2.1.7  | Buck/Boost Discontinuous and Continuous Mode | 17 |

| 1.2.2.1.8  | Synchronous and Asynchronous Conversion      | 18 |

| 1.2.2.1.9  | Two Stage Boost/Buck (Ćuk Converter)         | 19 |

| 1.2.2.1.10 | Two Stage Boost/Buck SEPIC Converter         | 21 |

| 1.2.2.1.11 | Two Stage Boost/Buck ZETA Converter          | 23 |

| 1.2.2.1.12 | Multiphase DC/DC Converters                  | 24 |

| 1.2.2.2    | Isolated DC/DC Converters                    | 26 |

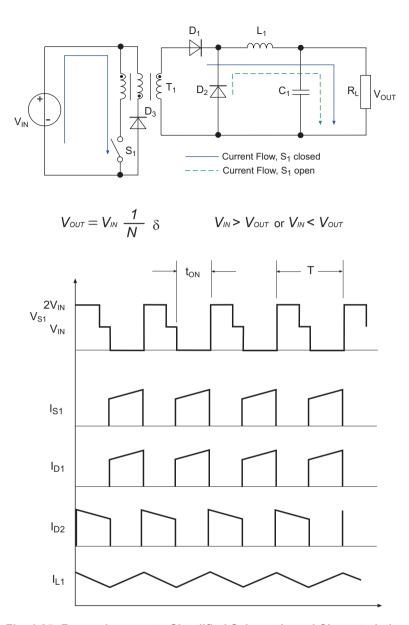

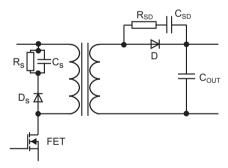

| 1.2.2.2.1  | Flyback DC/DC Converter                      | 26 |

| 1.2.2.2.2  | Forward DC/DC Converter                      | 28 |

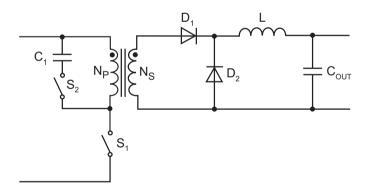

| 1.2.2.2.3  | Active Clamp Forward Converter               | 30 |

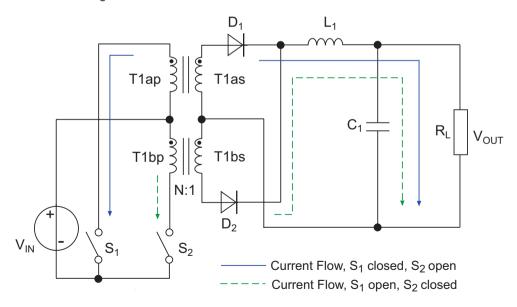

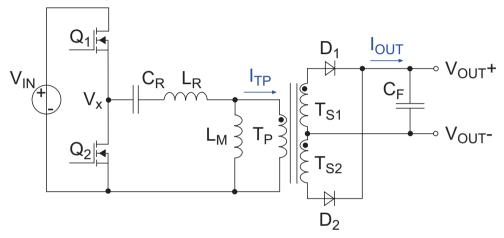

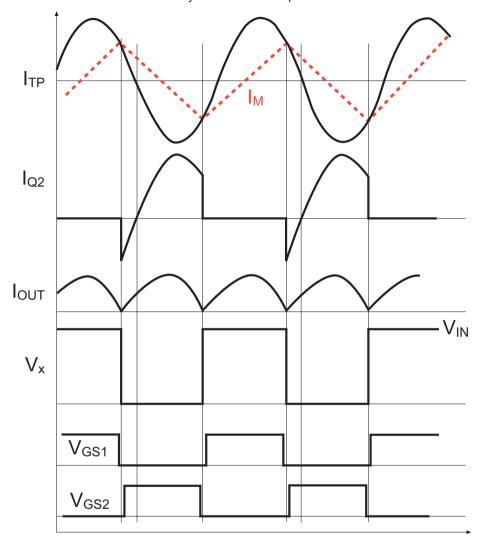

| 1.2.2.2.4  | Push-Pull Converter                          | 31 |

| 1.2.2.2.5  | Half Bridge and Full Bridge Converters       | 34 |

| 1.2.2.2.6  | Busconverter or Ratiometric Converter        | 35 |

| 1.2.2.2.7  | Unregulated Push-Pull Converter              | 36 |

| 1.2.3      | Parasitic Elements and their Effects         | 39 |

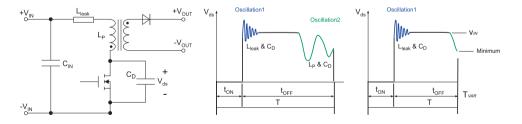

| 1.2.3.1    | QR Converter                                 | 42 |

| 1.2.3.2    | RM Converter                                 | 43 |

| 1.2.4      | Efficiency of DC/DC Converters               | 45 |

| 1.2.5      | PWM-Regulation Techniques                    | 46 |

| 1.2.6      | DC/DC Converter Regulation                   | 49 |

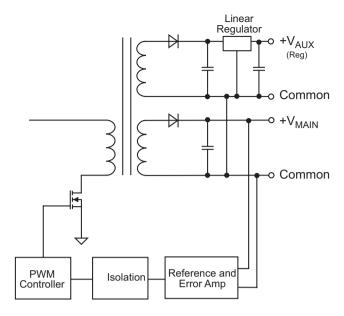

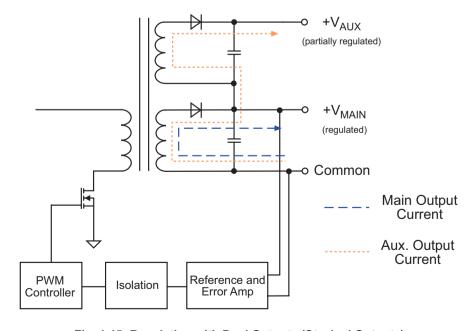

| 1.2.6.1    | Regulation of Multiple Outputs               | 49 |

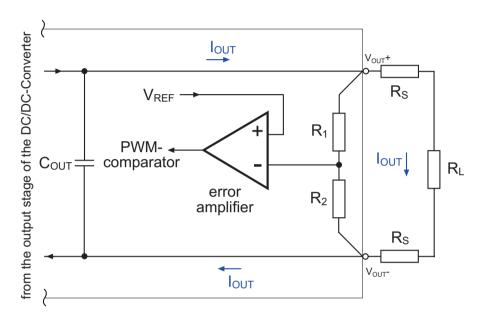

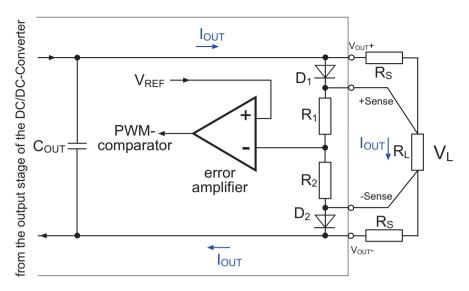

| 1.2.6.2    | Remote Sense                                 | 52 |

| 1.2.7      | Limitations on the Input Voltage Range       | 54 |

| 1.2.8      | Synchronous Rectification                    | 56 |

| 1.2.9      | Planar Transformers                          | 57 |

| 1.2.10     | Package Styles of DC/DC Converters           | 59 |

| 2.     | Feedback Loops                                                    | 61  |

|--------|-------------------------------------------------------------------|-----|

| 2.1    | Introduction                                                      | 61  |

| 2.2    | Open Loop Design                                                  | 61  |

| 2.3    | Closed Loops                                                      | 62  |

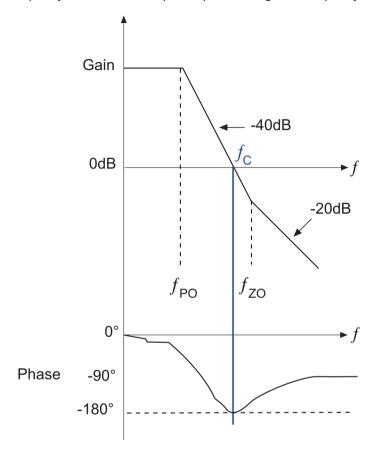

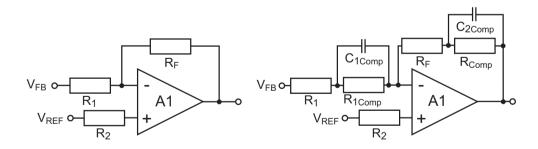

| 2.4    | Feedback Loop Compensation                                        | 65  |

| 2.4.1  | Right Half Plane Instability                                      | 67  |

| 2.5    | Slope Compensation                                                | 67  |

| 2.6    | Analyzing Loop Stability in Analogue and Digital Feedback Systems | 69  |

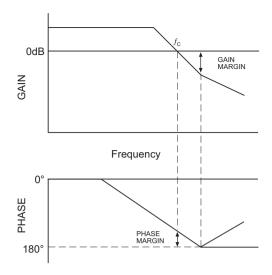

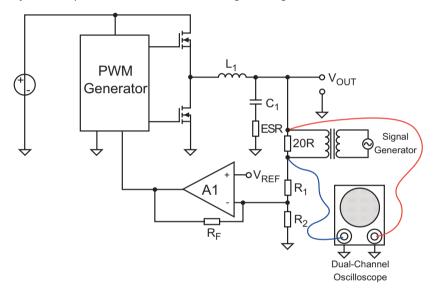

| 2.6.1  | Finding Analogue Loop Stability Experimentally                    | 69  |

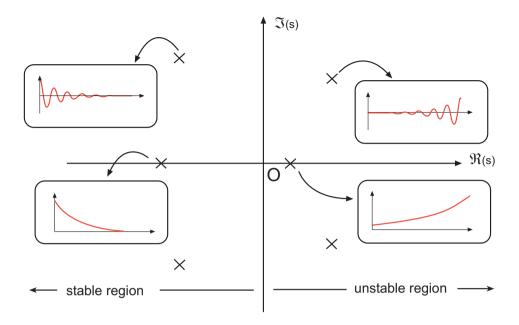

| 2.6.2  | Finding Analogue Loop Stability using the Laplace Transform       | 69  |

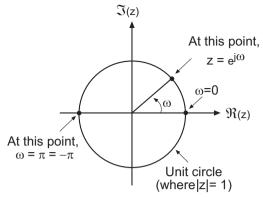

| 2.6.3  | Finding Digital Loop Stability using the Bilinear Transform       | 71  |

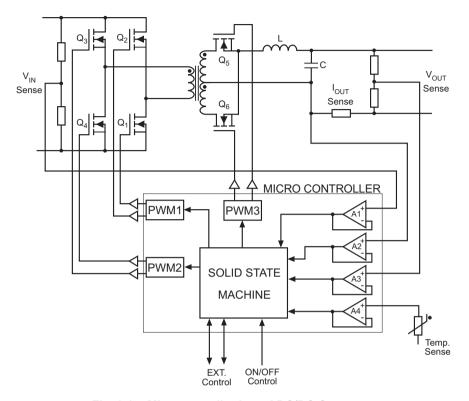

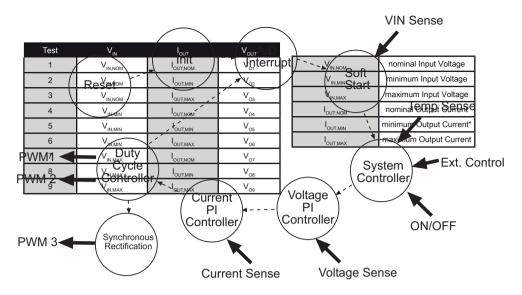

| 2.6.4  | Digital Feedback Loop                                             | 73  |

| 3.     | Understanding the Datasheet Parameters                            | 75  |

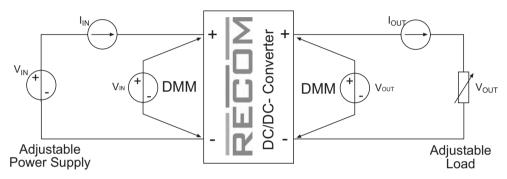

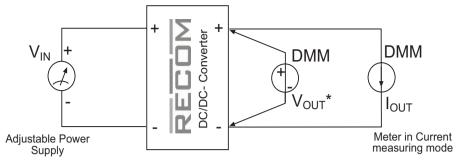

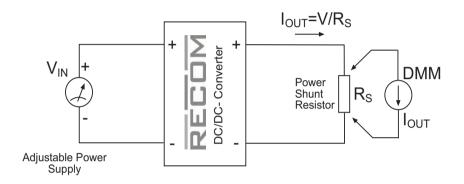

| 3.1    | Measurement Methods – DC Characteristic                           | 75  |

| 3.2    | Measurement Methods – AC Characteristics                          | 77  |

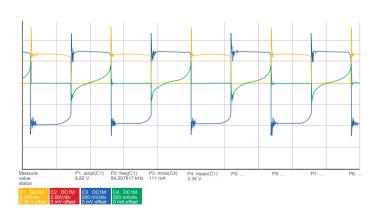

| 3.2.1  | Measuring Minimum and Maximum Duty Cycle                          | 78  |

| 3.2.2  | Output Voltage Accuracy                                           | 79  |

| 3.2.3  | Output Voltage Temperature Coefficient                            | 79  |

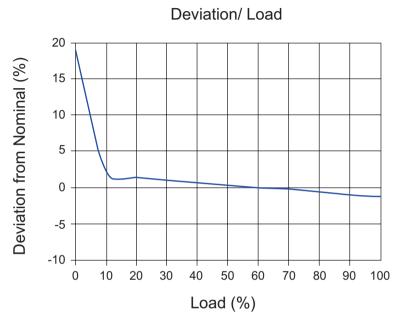

| 3.2.4  | Load Regulation                                                   | 80  |

| 3.2.5  | Cross Regulation                                                  | 81  |

| 3.2.6  | Line Regulation                                                   | 81  |

| 3.2.7  | Worst Case Output Voltage Accuracy                                | 82  |

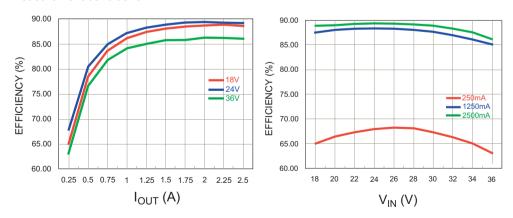

| 3.2.8  | Calculating Efficiency                                            | 82  |

| 3.2.9  | Input Voltage Range                                               | 83  |

| 3.2.10 | Input Current                                                     | 83  |

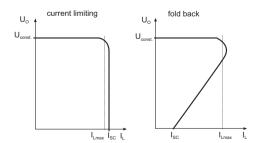

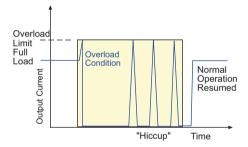

| 3.2.11 | Short Circuit and Overload Current                                | 85  |

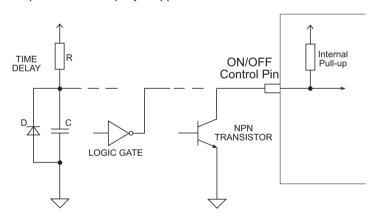

| 3.2.12 | Remote ON/OFF Control                                             | 86  |

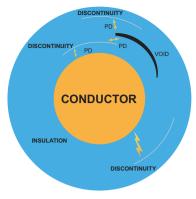

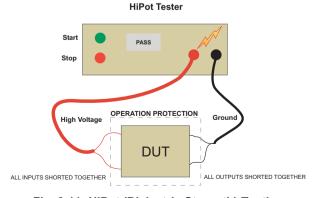

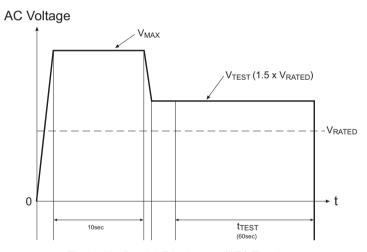

| 3.2.13 | Isolation Voltage                                                 | 87  |

| 3.2.14 | Isolation Resistance and Capacitance                              | 90  |

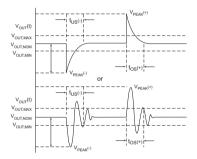

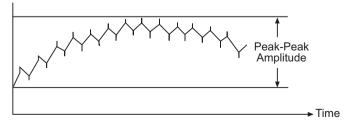

| 3.2.15 | Dynamic Load Response                                             | 91  |

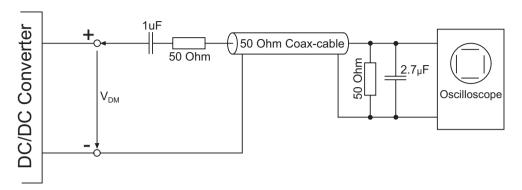

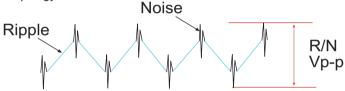

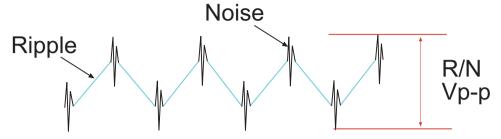

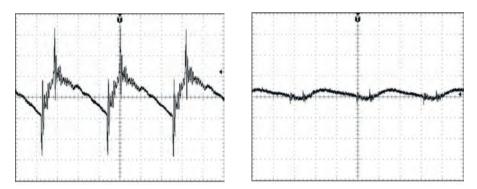

| 3.2.16 | Output Ripple/Noise                                               | 92  |

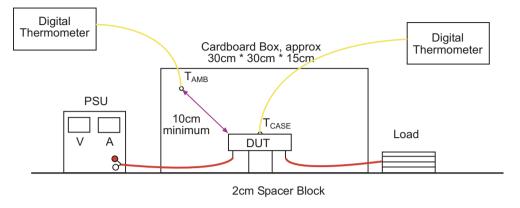

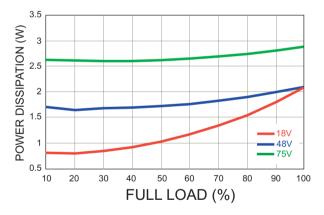

| 3.3    | Understanding Thermal Parameters                                  | 93  |

| 3.3.1  | Introduction                                                      | 93  |

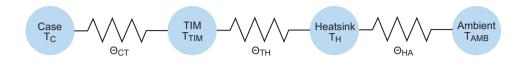

| 3.3.2  | Thermal Impedance                                                 | 94  |

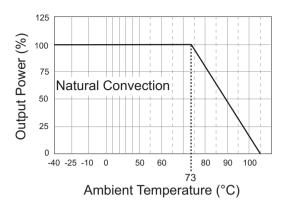

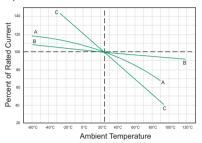

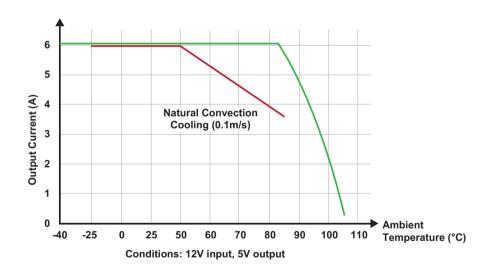

| 3.3.3  | Thermal Derating                                                  | 95  |

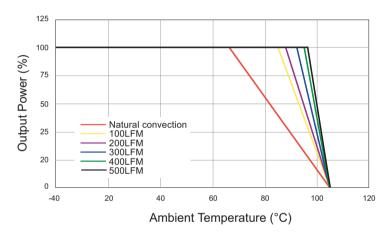

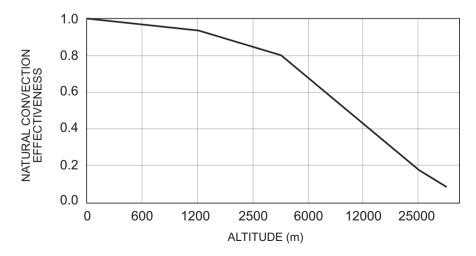

| 3.3.4  | Forced Cooling                                                    | 97  |

| 3.3.5  | Conducted and Radiated Cooling                                    | 98  |

| 4.     | DC/DC Converter Protections                                       | 100 |

| 4.1    | Introduction                                                      | 100 |

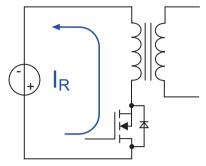

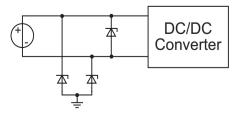

| 4.2    | Reverse Polarity Protection                                       | 100 |

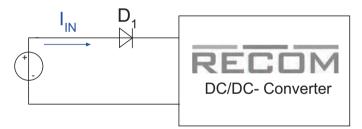

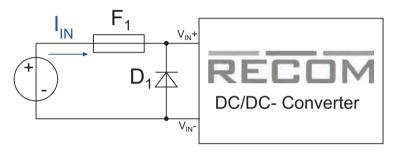

| 4.2.1  | Series Diode Reverse Polarity Protection                          | 101 |

| 4.2.2  | Shunt Diode Reverse Polarity Protection                           | 102 |

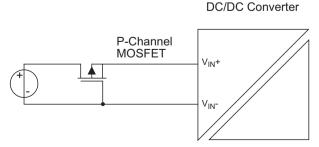

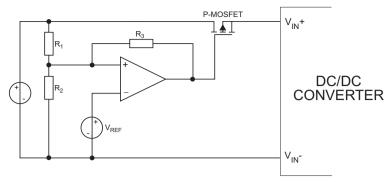

| 4.2.3   | P-FET Reverse Polarity Protection             | 102 |

|---------|-----------------------------------------------|-----|

| 4.3     | Input Fuse                                    | 103 |

| 4.4     | Output Over-Voltage Protection                | 104 |

| 4.5     | Input Over-Voltage Protection                 | 104 |

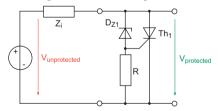

| 4.5.1   | SCR Crowbar Protection                        | 105 |

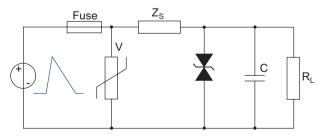

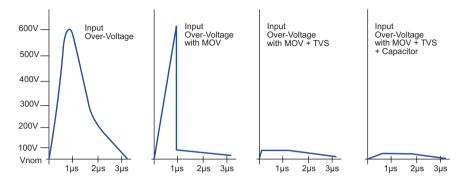

| 4.5.2   | Clamping Elements                             | 106 |

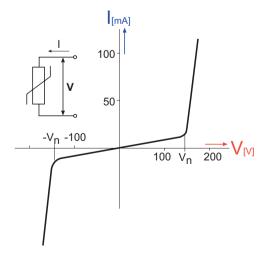

| 4.5.2.1 | Varistor                                      | 106 |

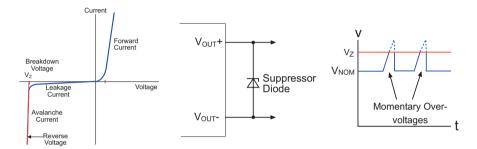

| 4.5.2.2 | Suppression Diode                             | 107 |

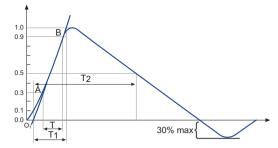

| 4.5.3   | OVP Using Several Elements                    | 108 |

| 4.5.4   | OVP Standards                                 | 109 |

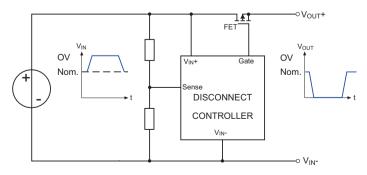

| 4.5.5   | OVP by Disconnection                          | 110 |

| 4.6     | Voltage Dips and Interruptions                | 111 |

| 4.7     | Inrush Current Limiting                       | 113 |

| 4.8     | Load Limiting                                 | 115 |

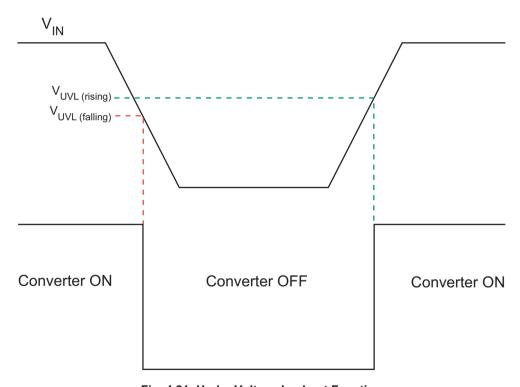

| 4.9     | Under Voltage Lockout                         | 116 |

| 5.      | Input and Output Filtering                    | 118 |

| 5.1     | Introduction                                  | 118 |

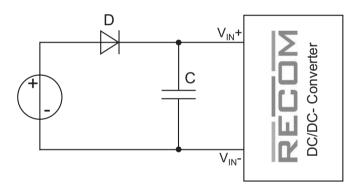

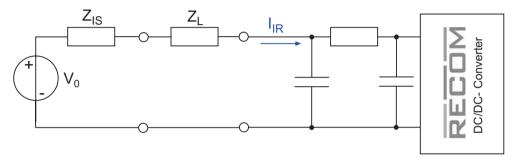

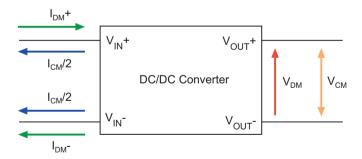

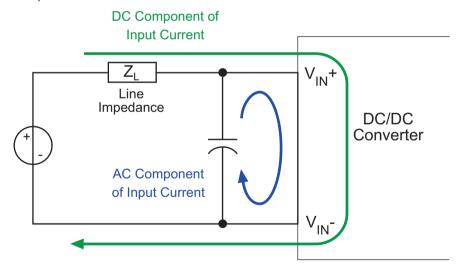

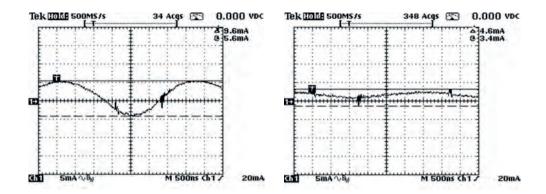

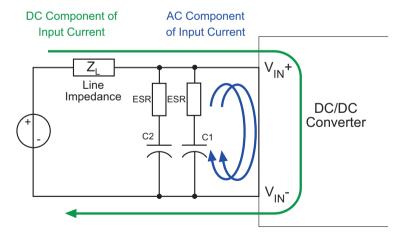

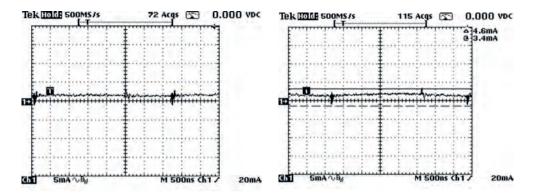

| 5.2     | Back Ripple Current                           | 119 |

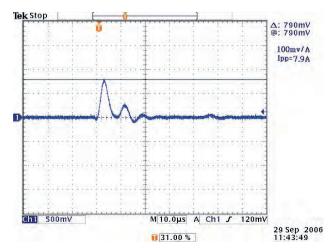

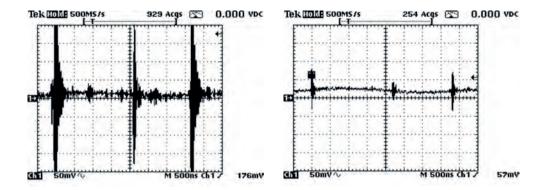

| 5.2.1   | Measuring Back Ripple Current                 | 119 |

| 5.2.2   | Back Ripple Current Countermeasures           | 120 |

| 5.2.3   | Input Capacitor Selection                     | 122 |

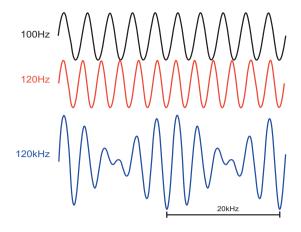

| 5.2.4   | Input Current of DC/DC Converters in Parallel | 123 |

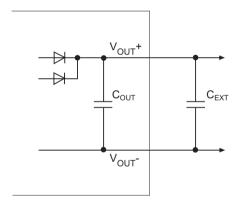

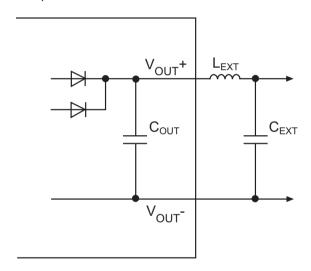

| 5.3     | Output Filtering                              | 125 |

| 5.3.1   | Differential Mode Output Filtering            | 125 |

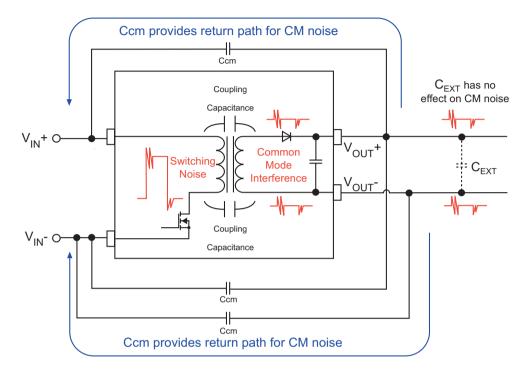

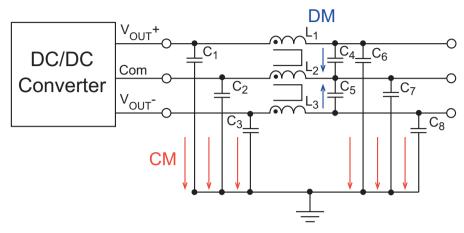

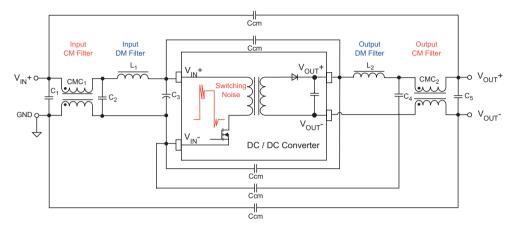

| 5.3.2   | Common Mode Output Filtering                  | 127 |

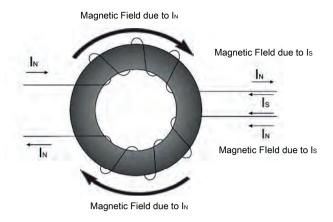

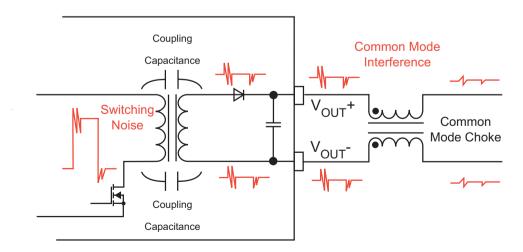

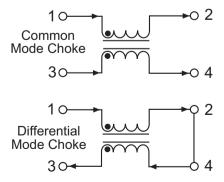

| 5.3.3   | Common Mode Chokes                            | 128 |

| 5.4     | Full Filtering                                | 132 |

| 5.4.1   | Filter PCB Layout                             | 133 |

| 6.      | Safety                                        | 136 |

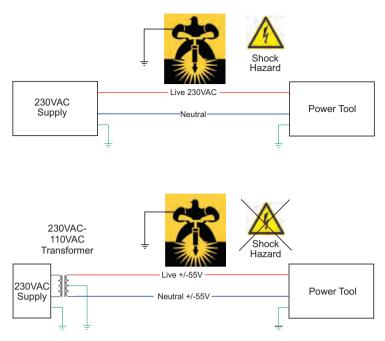

| 6.1     | Electric Shock                                | 137 |

| 6.1.1   | Insulation Class                              | 137 |

| 6.1.2   | Human Body Treshold Currents                  | 138 |

| 6.1.3   | Protection from Electric Shock                | 140 |

| 6.1.4   | Protective Earth                              | 143 |

| 6.2     | Hazardous Energy                              | 145 |

| 6.2.1   | Fuses                                         | 145 |

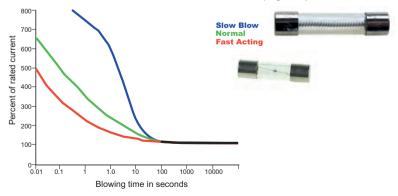

| 6.2.1.1 | Fuse Reaction Time and Inrush Currents        | 147 |

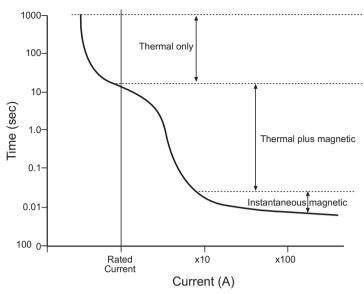

| 6.2.2   | Circuit Breakers                              | 148 |

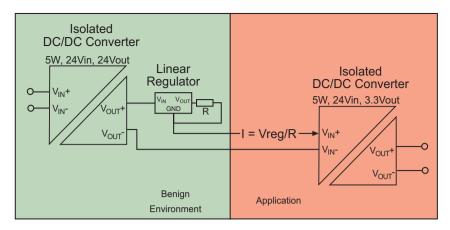

| 6.3     | Inherent Safety                               | 149 |

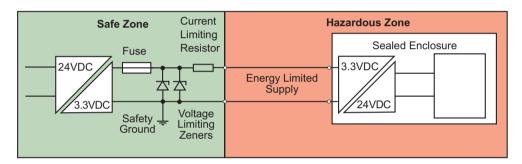

| 6.4     | Intrinsic Safety                              | 150 |

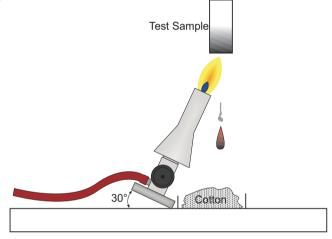

| 6.4.1   | Combustible Materials                         | 151 |

| 6.4.2   | Smoke                                         | 153 |

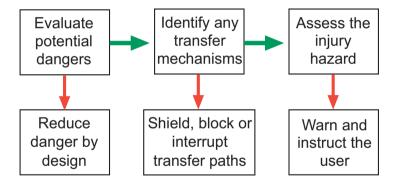

| 6.5   | Injury Hazards                                                      | 154 |

|-------|---------------------------------------------------------------------|-----|

| 6.5.1 | Hot Surfaces                                                        | 154 |

| 6.5.2 | Sharp Edges                                                         | 154 |

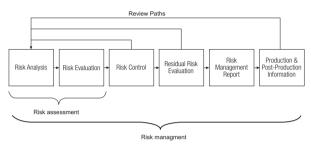

| 6.6   | Designing for Safety                                                | 155 |

| 6.6.1 | FMEA                                                                | 157 |

| 6.7   | Medical Safety                                                      | 159 |

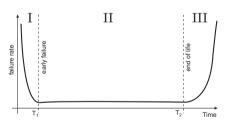

| 7.    | Reliability                                                         | 161 |

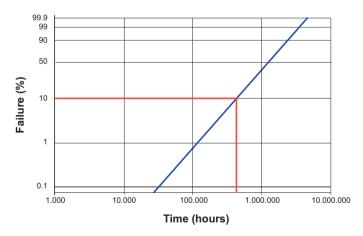

| 7.1   | Reliability Prediction                                              | 161 |

| 7.2   | Environmental Stress Factor                                         | 164 |

| 7.3   | Using MTBF Figures                                                  | 165 |

| 7.4   | Demonstrated MTBF                                                   | 166 |

| 7.5   | MTBF and Temperature                                                | 167 |

| 7.6   | Designing for Reliability                                           | 168 |

| 7.7   | PCB Layout Reliability Consideration                                | 169 |

| 7.8   | Capacitor Reliability                                               | 173 |

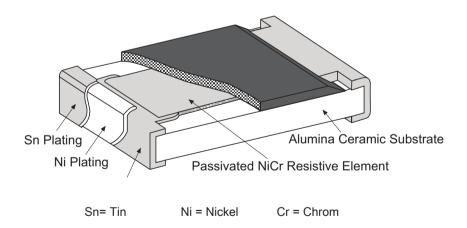

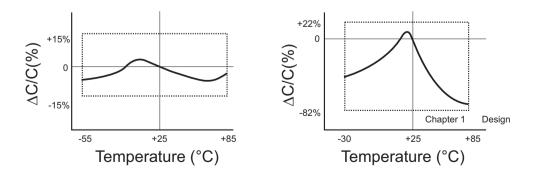

| 7.8.1 | MLCC                                                                | 173 |

| 7.8.2 | Tantalum and Electrolytic Capacitors                                | 176 |

| 7.9   | Semiconductors Reliability                                          | 179 |

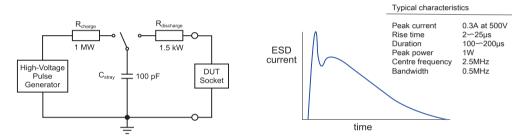

| 7.10  | ESD                                                                 | 180 |

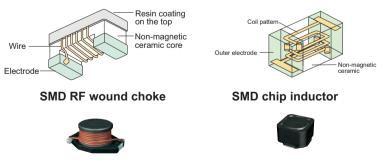

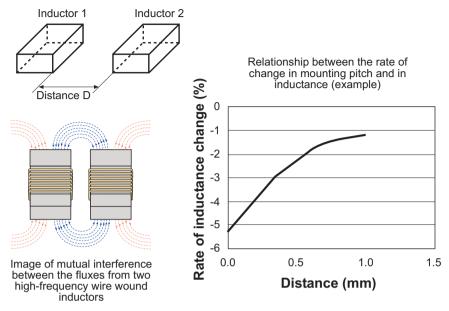

| 7.11  | Inductors                                                           | 182 |

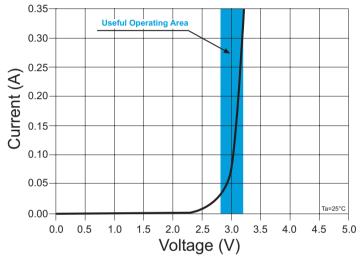

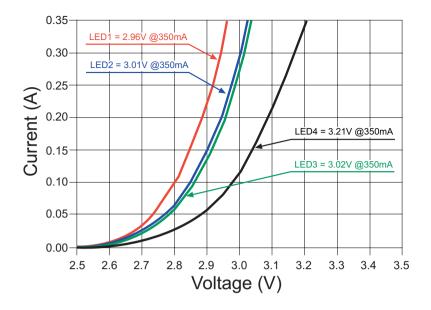

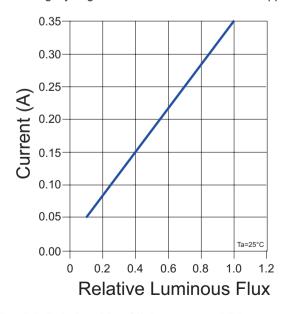

| 8.    | LED Characteristics                                                 | 184 |

| 8.1   | Driving LEDs with Constant Currents                                 | 186 |

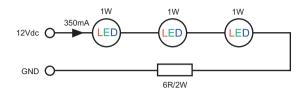

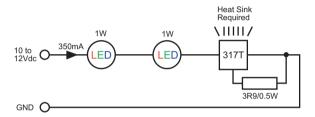

| 8.2   | Some DC Constant Current Sources                                    | 186 |

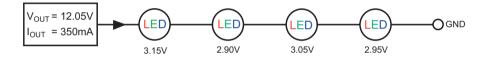

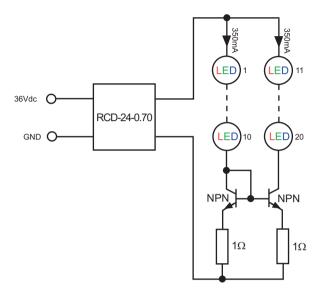

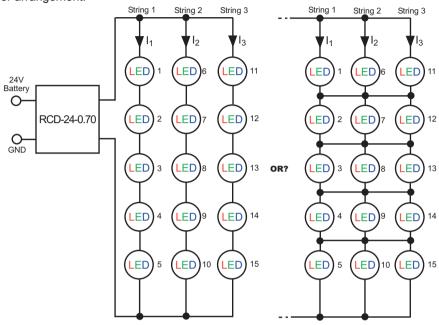

| 8.3   | Connecting LEDs in String                                           | 188 |

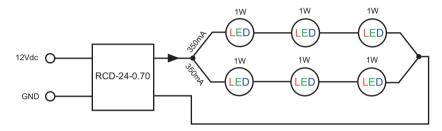

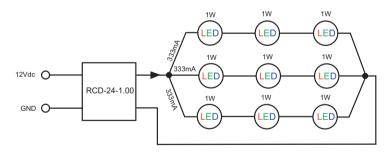

| 8.4   | Connecting LED Strings in Parallel                                  | 189 |

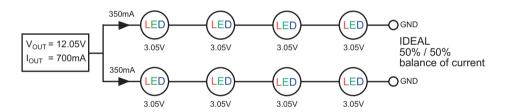

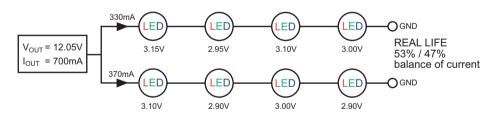

| 8.5   | Balancing LED Current in Parallel Strings                           | 190 |

| 8.6   | Parallel Strings or Grid Array – Which is better?                   | 192 |

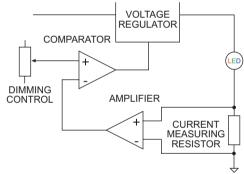

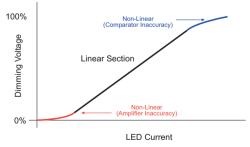

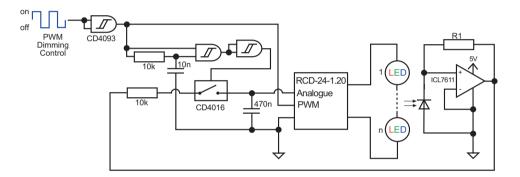

| 8.7   | LED Dimming                                                         | 194 |

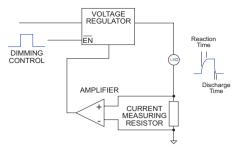

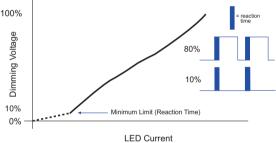

| 8.7.1 | Analogue versus PWM Dimming                                         | 194 |

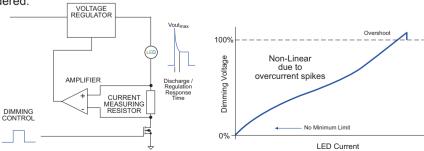

| 8.7.2 | Perceived Brightness                                                | 196 |

| 8.7.3 | Dimming Conclusion                                                  | 196 |

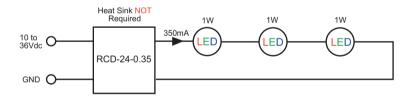

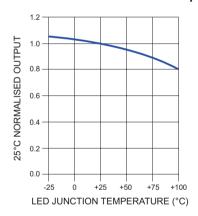

| 8.8   | Thermal Considerations                                              | 197 |

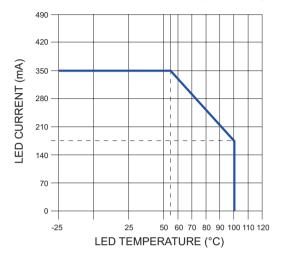

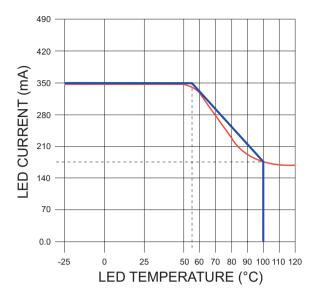

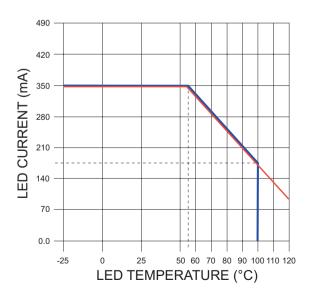

| 8.9   | Temperature Derating                                                | 198 |

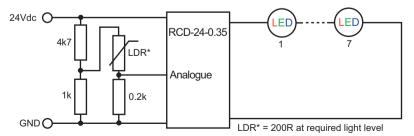

| 8.9.1 | Adding Automatic Thermal Derating to an LED Driver                  | 198 |

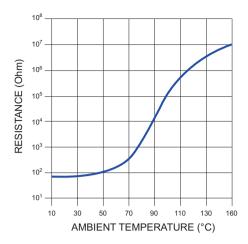

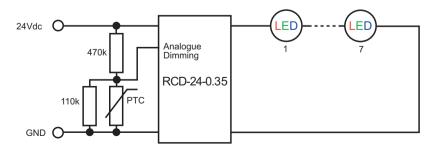

| 8.9.2 | Over-temperature Protection using a PTC Thermistor                  | 198 |

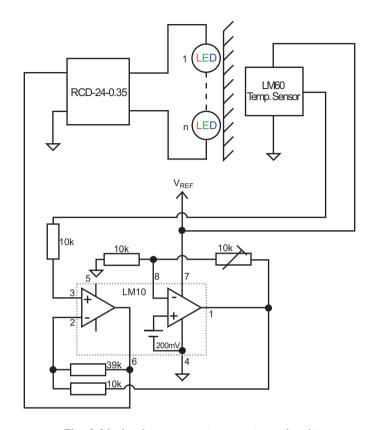

| 8.9.3 | Over-temperature Protection using an Analogue Temperature Sensor IC | 200 |

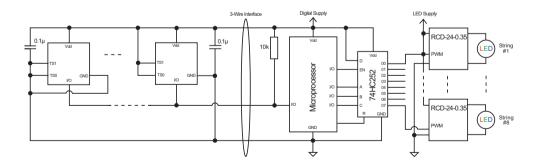

| 8.9.4 | Over-temperature Protection using a Microcontroller                 | 202 |

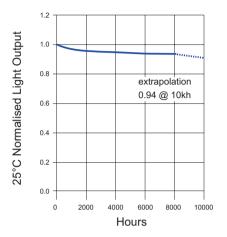

| 8.10  | Brightness Compensation                                             | 203 |

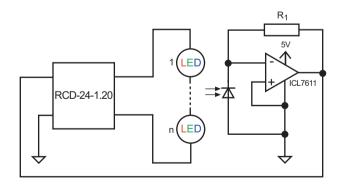

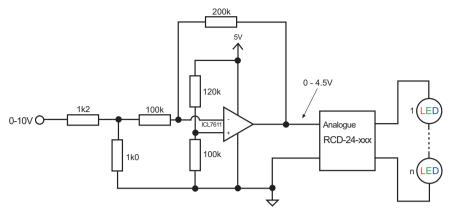

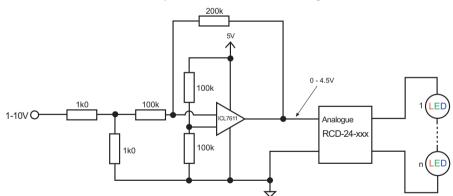

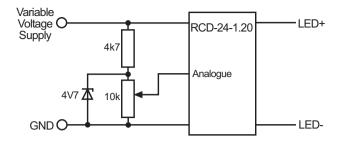

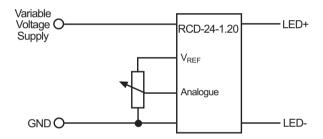

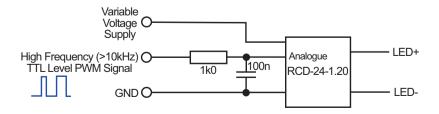

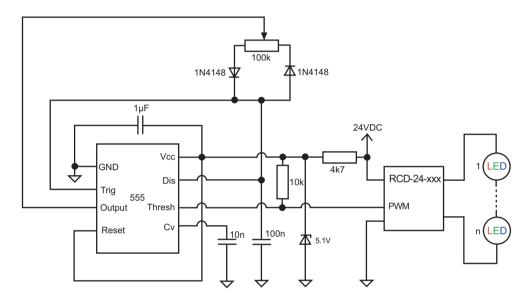

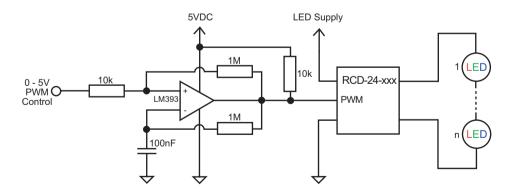

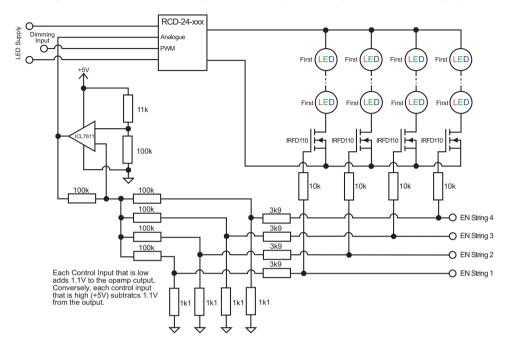

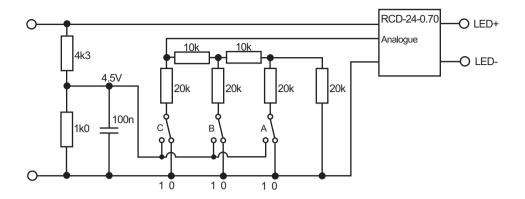

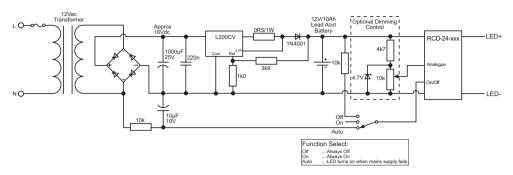

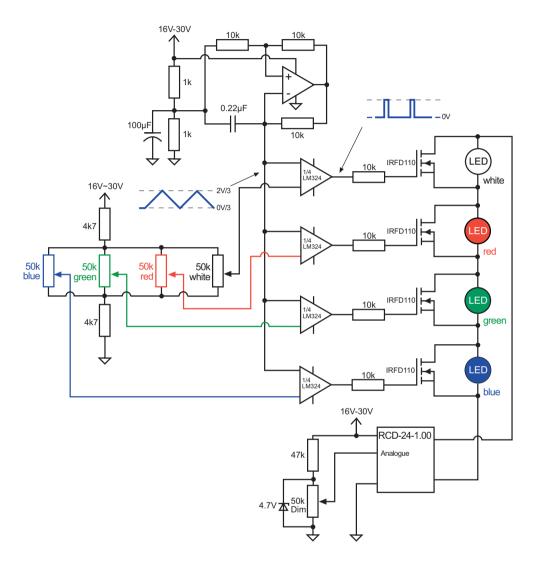

| 8.11  | Some Circuit Ideas using RCD driver                                 | 205 |

| 9.    | Applications                                                        | 212 |

| 9.1   | Introduction                                                        | 212 |

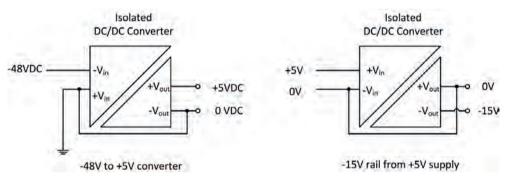

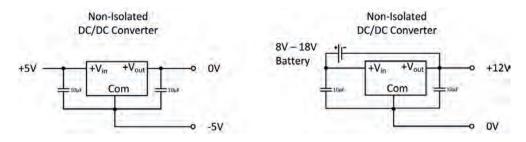

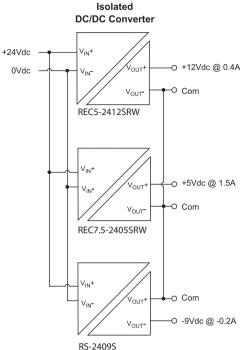

| 9.2      | Polarity Inversion                                  | 212 |

|----------|-----------------------------------------------------|-----|

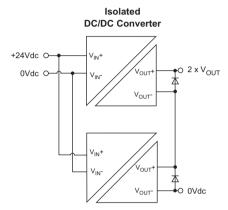

| 9.3      | Power Doubler                                       | 213 |

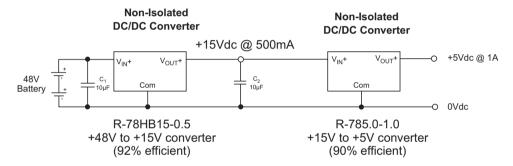

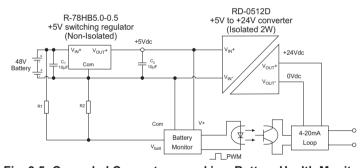

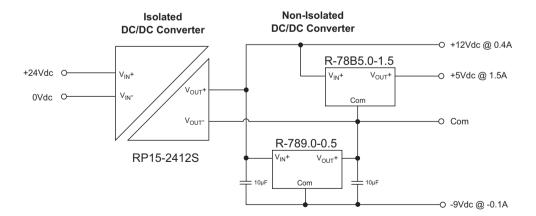

| 9.4      | Combining Switching Regulators and DC/DC Converters | 214 |

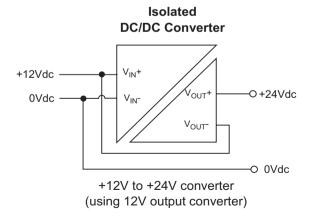

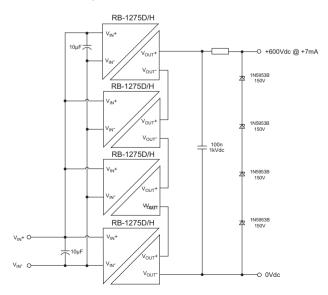

| 9.5      | Connecting Converters in Series                     | 217 |

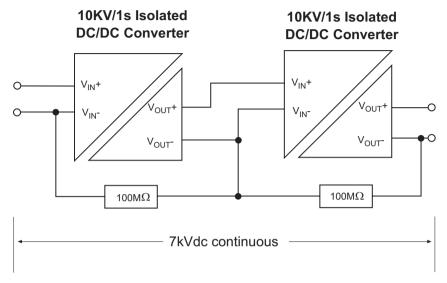

| 9.6      | Increasing the Isolation                            | 218 |

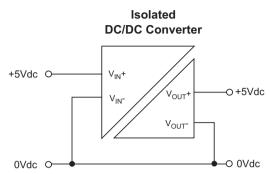

| 9.7      | 5V Rail Clean-up                                    | 218 |

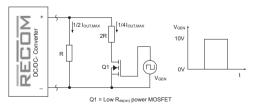

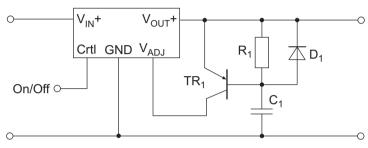

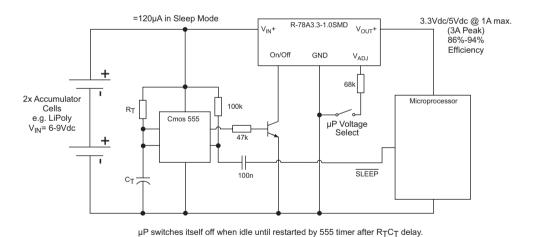

| 9.8      | Using CTRL Pin                                      | 220 |

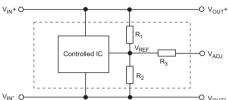

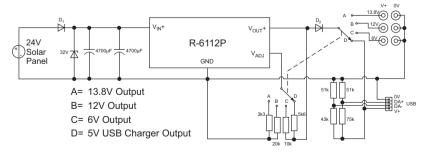

| 9.9      | Using V <sub>ADJ</sub> Pin                          | 221 |

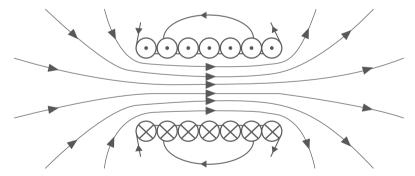

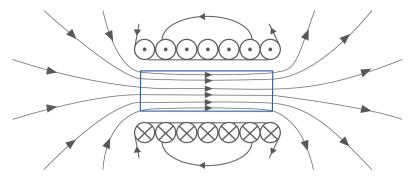

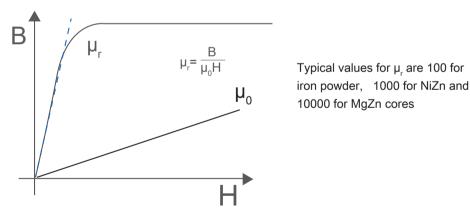

| 10.      | Introduction to Magnetics                           | 222 |

| 10.1     | Basics                                              | 222 |

| 10.1.1   | Core Saturation                                     | 225 |

| 10.1.2   | Air-gapped Inductors                                | 228 |

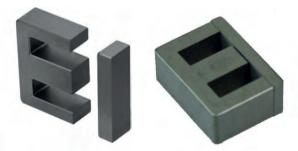

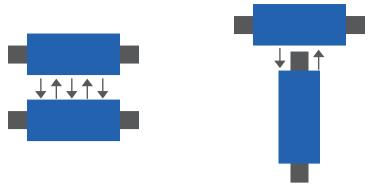

| 10.1.3   | Core Shapes                                         | 230 |

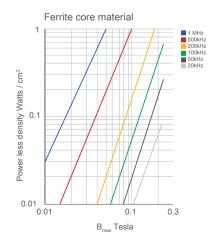

| 10.1.4   | Core Losses                                         | 232 |

| 10.1.4.1 | Mutual Inductance Losses                            | 232 |

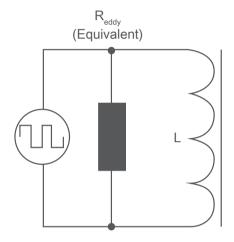

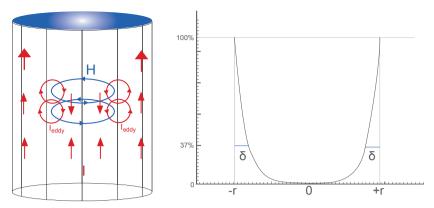

| 10.1.4.2 | Eddy Current Losses                                 | 233 |

| 10.1.4.3 | The Skin Effect                                     | 234 |

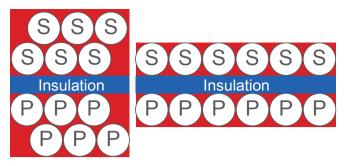

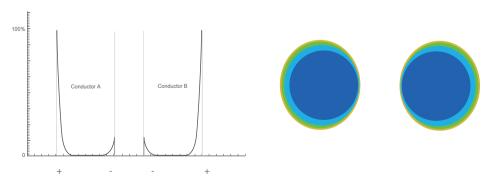

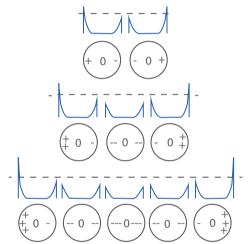

| 10.1.4.4 | The Proximity Effect                                | 237 |

| 10.2     | Buck Converter Design Worked Example                | 240 |

| 10.2.1   | Calculating the Losses in a Buck Converter          | 242 |

| 10.2.1.1 | Inductor Losses                                     | 242 |

| 10.2.1.2 | Calculating the MOSFET Loss                         | 244 |

| 10.2.1.3 | Calculating the Diode Loss                          | 245 |

| 10.2.2   | Boost Converter Design                              | 245 |

| 10.3     | Introduction to Transformers                        | 246 |

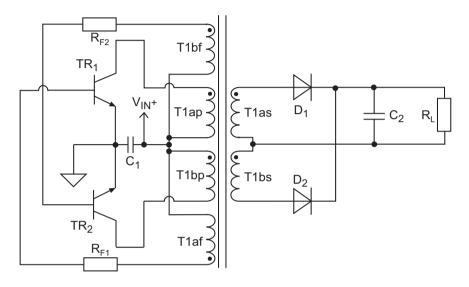

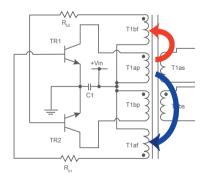

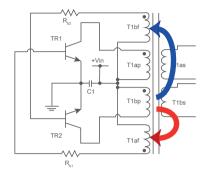

| 10.3.1   | Royer Push-Pull Self Oscillating Transformer        | 246 |

| 10.3.2   | Royer Transformer Design Considerations             | 249 |

| 10.3.3   | Transformer Design Considerations                   | 250 |

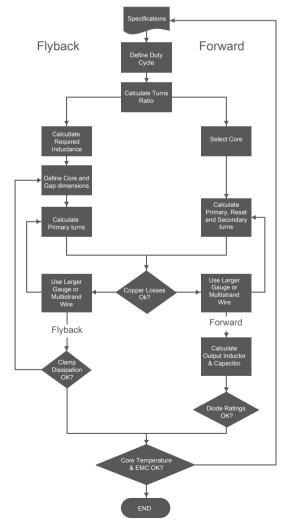

| 10.3.4   | Forward Converter Transformer Design                | 251 |

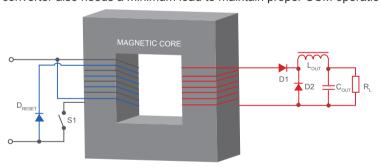

| 10.3.4.1 | Introduction to Forward Converters                  | 251 |

| 10.3.4.2 | Forward Converter Transformer Design                | 252 |

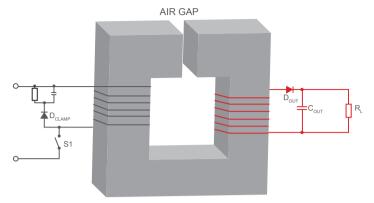

| 10.3.5   | Flyback Transformer Design                          | 255 |

| 10.3.5.1 | Flyback Clamp Circuit and Associated Losses         | 263 |

| 10.3.5.2 | Transformer Design for Quasi-Resonant Flyback Mode  | 265 |

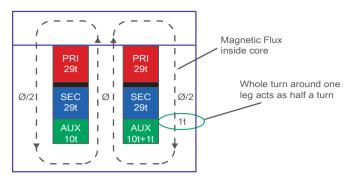

| 10.4     | Whole turns and fractional turns                    | 266 |

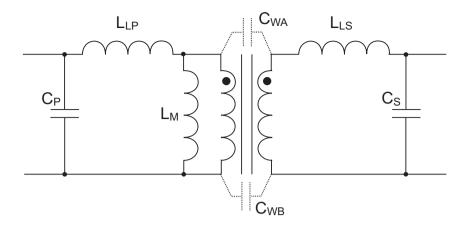

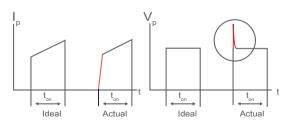

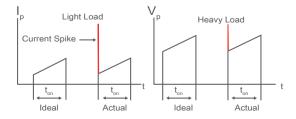

| 10.4.1   | Transformer Leakage Inductance and Capacitance      | 267 |

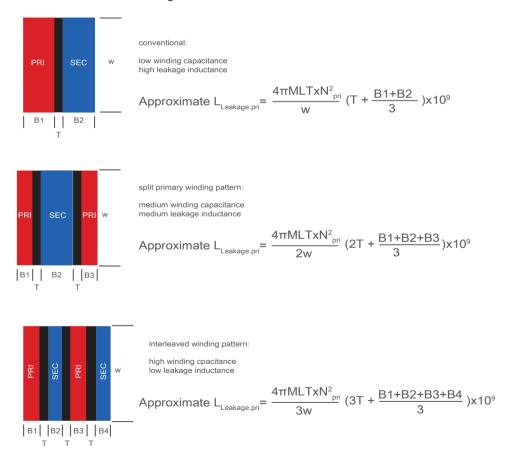

| 10.4.2   | Methods of reducing Transformer Leakage Inductance  | 268 |

| 10.4.3   | Methods of reducing Transformer Leakage Capacitance | 270 |

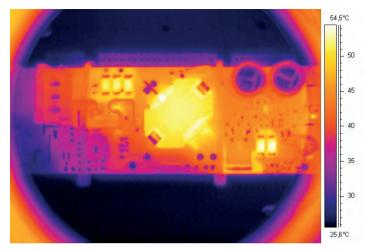

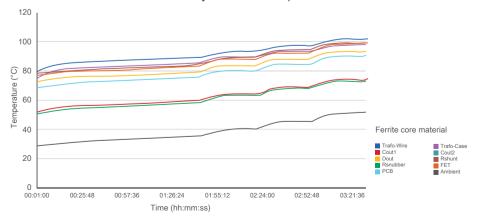

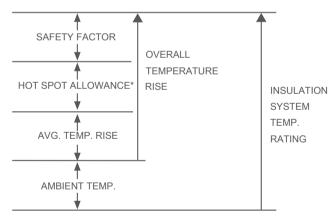

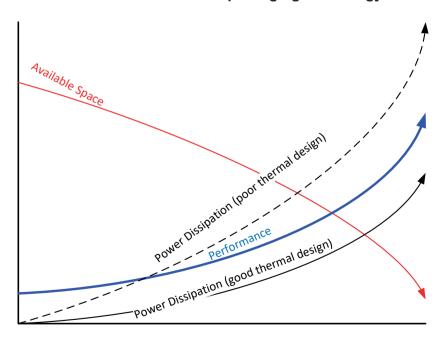

| 10.5     | Transformer Core Temperature                        | 271 |

| 10.6     | Finalizing the Transformer Design: EMI              | 274 |

|          |                                                     |     |

| 11.1.Introduction27611.2.The need for advanced packaging technology27711.3.Packaging technologies27911.3.1.Through hole27911.3.2.Conventional SMD (Gull wing pins)27911.3.3.QFN Chip carrier28111.3.4.Solder Ball28211.4.PCB substrate technology28411.5.Stacked components28711.6.Embedded components28811.6.1.Embedded Magnetics28811.6.2.Embedded active and passive components28911.7.Conclusion290References and Further Reading292Application Guides and Notes293Acknowledgements294                                                                                                                                                                                                                          | 11.              | Advanced Assembly and Packaging            | 276 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------|-----|

| 11.3.       Packaging technologies       279         11.3.1.       Through hole       279         11.3.2.       Conventional SMD (Gull wing pins)       279         11.3.3.       QFN Chip carrier       281         11.3.4.       Solder Ball       282         11.4.       PCB substrate technology       284         11.5.       Stacked components       287         11.6.       Embedded components       288         11.6.1.       Embedded Magnetics       288         11.6.2.       Embedded active and passive components       289         11.7.       Conclusion       290         References and Further Reading       292         Application Guides and Notes       292         About RECOM       293 | 11.1.            | Introduction                               | 276 |

| 11.3.1. Through hole 279 11.3.2. Conventional SMD (Gull wing pins) 279 11.3.3. QFN Chip carrier 281 11.3.4. Solder Ball 282 11.4. PCB substrate technology 284 11.5. Stacked components 287 11.6. Embedded components 288 11.6.1. Embedded Magnetics 288 11.6.2. Embedded active and passive components 289 11.7. Conclusion 290  References and Further Reading 292 Application Guides and Notes 293                                                                                                                                                                                                                                                                                                               | 11.2.            | The need for advanced packaging technology | 277 |

| 11.3.2.       Conventional SMD (Gull wing pins)       279         11.3.3.       QFN Chip carrier       281         11.3.4.       Solder Ball       282         11.4.       PCB substrate technology       284         11.5.       Stacked components       287         11.6.       Embedded components       288         11.6.1.       Embedded Magnetics       288         11.6.2.       Embedded active and passive components       289         11.7.       Conclusion       290         References and Further Reading       292         Application Guides and Notes       293         About RECOM       293                                                                                                   | 11.3.            | Packaging technologies                     | 279 |

| 11.3.3.QFN Chip carrier28111.3.4.Solder Ball28211.4.PCB substrate technology28411.5.Stacked components28711.6.Embedded components28811.6.1.Embedded Magnetics28811.6.2.Embedded active and passive components28911.7.Conclusion290References and Further Reading292Application Guides and Notes292About RECOM293                                                                                                                                                                                                                                                                                                                                                                                                    | 11.3.1.          | Through hole                               | 279 |

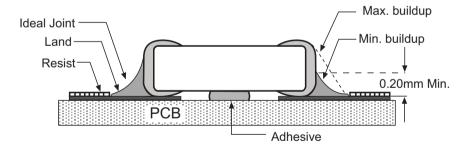

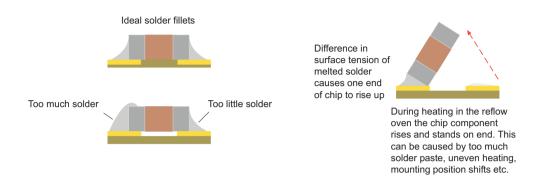

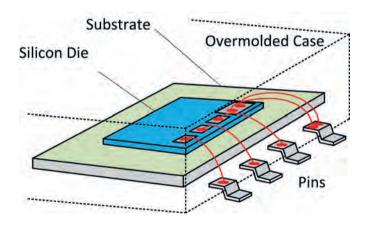

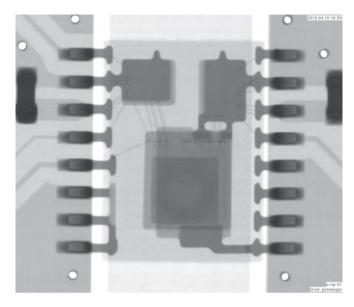

| 11.3.4.Solder Ball28211.4.PCB substrate technology28411.5.Stacked components28711.6.Embedded components28811.6.1.Embedded Magnetics28811.6.2.Embedded active and passive components28911.7.Conclusion290References and Further Reading292Application Guides and Notes292About RECOM293                                                                                                                                                                                                                                                                                                                                                                                                                              | 11.3.2.          | Conventional SMD (Gull wing pins)          | 279 |

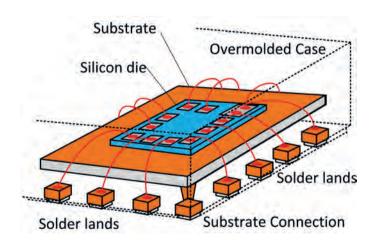

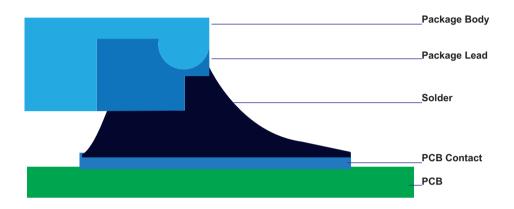

| 11.4. PCB substrate technology 284 11.5. Stacked components 287 11.6. Embedded components 288 11.6.1. Embedded Magnetics 288 11.6.2. Embedded active and passive components 289 11.7. Conclusion 290  References and Further Reading 292 Application Guides and Notes 293 About RECOM 293                                                                                                                                                                                                                                                                                                                                                                                                                           | 11.3.3.          | QFN Chip carrier                           | 281 |

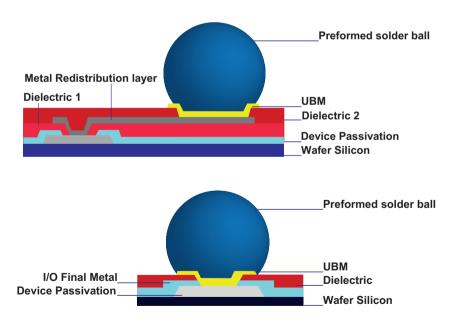

| 11.5. Stacked components 287 11.6. Embedded components 288 11.6.1. Embedded Magnetics 289 11.6.2. Embedded active and passive components 289 11.7. Conclusion 290  References and Further Reading 292 Application Guides and Notes 293 About RECOM 293                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 11.3.4.          | Solder Ball                                | 282 |

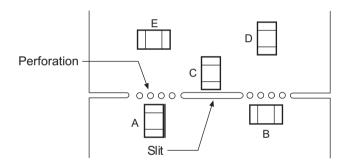

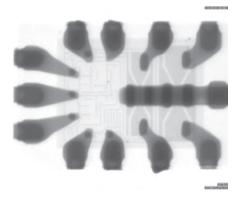

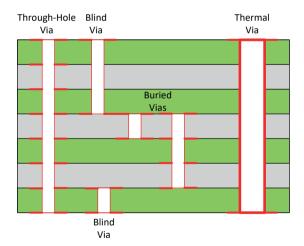

| 11.6. Embedded components 288 11.6.1. Embedded Magnetics 288 11.6.2. Embedded active and passive components 289 11.7. Conclusion 290  References and Further Reading 292 Application Guides and Notes 293 About RECOM 293                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 11.4.            | PCB substrate technology                   | 284 |

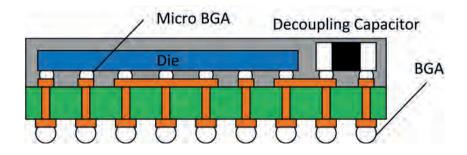

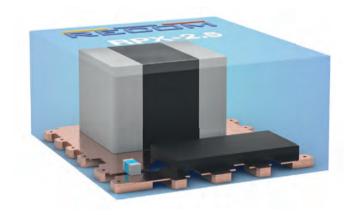

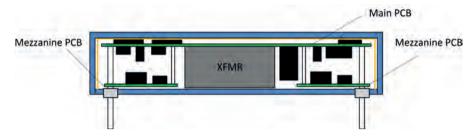

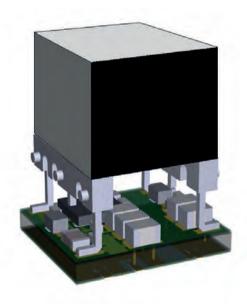

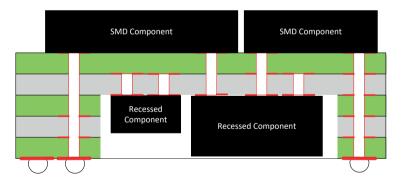

| 11.6.1. Embedded Magnetics 288 11.6.2. Embedded active and passive components 289 11.7. Conclusion 290  References and Further Reading 292 Application Guides and Notes 293 About RECOM 293                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11.5.            | Stacked components                         | 287 |

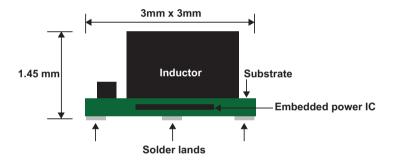

| 11.6.2. Embedded active and passive components 289 11.7. Conclusion  References and Further Reading 292 Application Guides and Notes 292 About RECOM 293                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 11.6.            | Embedded components                        | 288 |

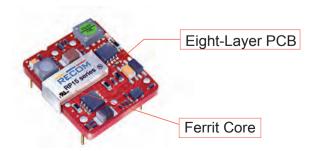

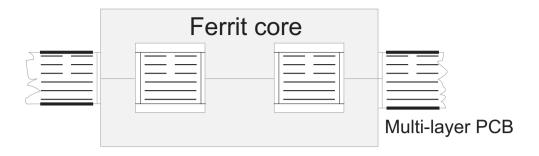

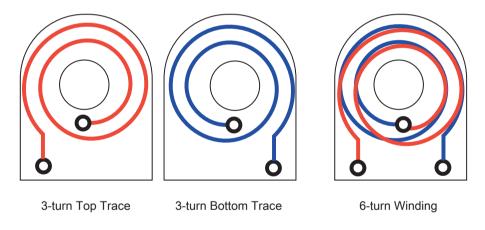

| 11.7. Conclusion 290  References and Further Reading 292  Application Guides and Notes 292  About RECOM 293                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11.6.1.          | Embedded Magnetics                         | 288 |

| References and Further Reading 292 Application Guides and Notes 292 About RECOM 293                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 11.6.2.          | Embedded active and passive components     | 289 |

| Application Guides and Notes 292 About RECOM 293                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11.7.            | Conclusion                                 | 290 |

| About RECOM 293                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Referen          | ces and Further Reading                    | 292 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ••               |                                            |     |

| Acknowledgements 294                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |                                            |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Acknowledgements |                                            | 294 |

## 1. Introduction to Power Regulation

Modern AC/DC and DC/DC converters are designed to provide efficient power conversion to deliver a controlled, safe and well-regulated DC power supply for a variety of electronic instruments, devices and systems. It's not all too long ago that a transformer, rectifier and linear regulator was the main technology in power conversion, but just as the LED is slowly replacing the light bulb, so is the DC/DC converter gradually edging out the linear regulator and the primary-side switching controller is replacing the simple 50Hz mains transformer. In the past decade there has been of immense technical progress the development of switching regulators to allow the benefits of new circuits, components, and materials that previously simply did not exist before. This progress has made it possible to increase the performance and to improve the thermal behavior, while simultaneously substantially reducing the size, weight and cost of power supplies. Consequently, switching regulators are used today in large numbers and are the standard technology in both DC/DC and AC/DC power conversion.

## 1.1 Linear Regulators

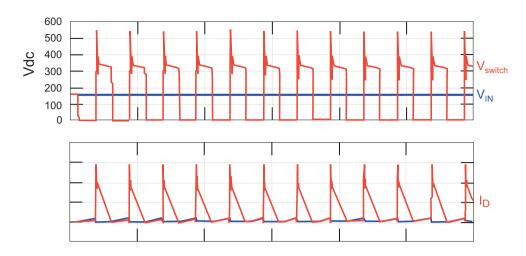

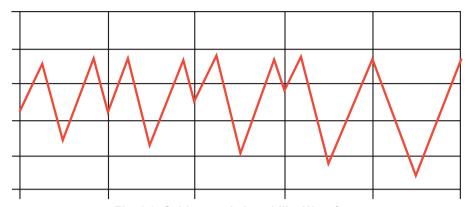

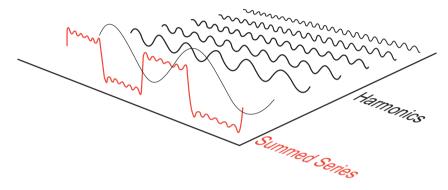

Linear voltage regulators deliver a stable output voltage from a more or less stable input voltage source. In normal operation, even if the input voltage fluctuates rapidly, the output voltage remains stable. This means they can also very effectively filter out input ripple, not only at the fundamental frequency, but also as far as the fifth or tenth harmonic. The limitation is only the reaction speed of the internal error amplifier feedback circuit.

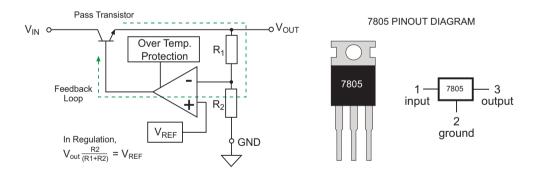

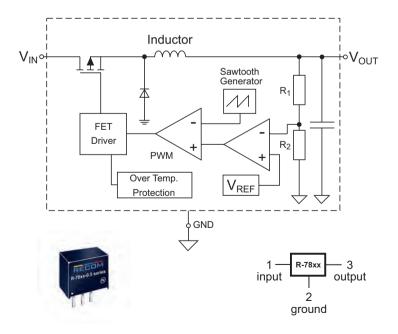

Fig. 1.1: 3-Pin Linear Regulator Block Diagram and Pinout

Most linear regulators have a closed loop control. Fig. 1.1 illustrates this type of voltage regulation. The pass transistor is the regulatory element, effectively a variable resistor that limits the current flowing from input to output. The resistor divider chain  $R_1/R_2$  is chosen so that at the required output voltage, the divided down voltage at the error amp inverting input is the same as the VREF voltage at the non-inverting input. The error amplifier controls its output in such a way that the voltage difference between its inputs is always zero.

If the voltage at the output increases due to a reduction in the load or an increased input voltage, the voltage at the inverting input of the error amplifier rises higher than  $V_{REF}$  voltage and the output of the error amplifier is lowered, so reducing the drive to the pass transistor and reducing the output voltage. Alternatively, if the load increases or the input voltage drops, the voltage at the inverting input sinks below the  $V_{REF}$  voltage and the drive to the transistor is increased to raise the output voltage to compensate. Thus the same feedback loop regulates for both input voltage variations (line regulation) and changes in load (load regulation). It need not be specially emphasized that the reference voltage must be very stable and have an excellent temperature coefficient to give a stable and accurate output voltage, but with a good PCB layout an output voltage ripple/noise value of less than  $50\mu Vp$ -p is easily possible.

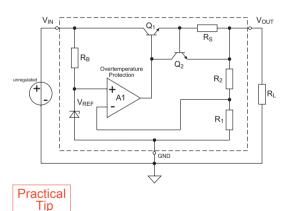

The Fig. 1.1 simplified 3-pin regulator block diagram does not show the short circuit protection. If the output is shorted to ground, the transistor would be turned hard on and a very high current would flow from input to output, so a second internal circuit is needed to limit the current (Fig 1.2). The current limiting uses the voltage drop across the sense resistor,  $R_{\rm S}$  to monitor the ouput current. When the current is high enough so that the voltage exceeds 0.7V,  $Q_{\rm S}$  starts to conduct to "steal" current away from  $Q_{\rm S}$ , thus reducing the drive and limiting the output current, thus  $I_{\rm LIMIT} = 0.7 \text{V/RS}$ .

The current limit needs to be set well above the maximum current that would flows during normal operation. Typically the limit is 150% - 200% higher than the rated current. As the regulator is not disabled during a short circuit, it is in constant overload. Some low cost linear regulators simply rely on the thermal protection circuit to shut down the pass transistor before it burns out as the "short circuit protection". This may protect the linear regulator, but the primary power supply may overheat and fail if it is not dimensioned to deliver the short circuit current during the time it takes for the regulator to switch itself off.

Fig. 1.2: Linear regulator with current limiting ("short circuit protection")

The difference between input and output voltage is dropped by the pass transistor. If, for example, the input voltage is 12V (say from a car battery) and the regulated output voltage is 5V, then 7V has to be dropped by the transistor. This means more power is dissipated in the regulator than is actually delivered to the load (see also the discussion of efficiency calculation in the next section). This is why most linear regulators need a heat sink. Obviously, if the input voltage drops below the output voltage, the linear regulator cannot compensate and the

output voltage will follow the input voltage down. However if the input voltage drops too low, the internal power supply to the error amplifier and  $V_{\text{REF}}$  will be compromised and output may become unstable or start to oscillate.

Linear regulators also perform poorly in stand-by. Even if no load is applied, a typical 78xx series regulator still needs around 5mA to power the error amp and reference voltage circuits. If the input voltage is 24V, this guiescent current means a no load consumption of 120mW.

The advantages of linear regulators are low cost, good control characteristics, low noise, low emissions and excellent transient response. The disadvantages are high quiescent consumption, only single outputs and extremely low efficiency for large input/output voltage differences.

#### 1.1.1 Efficiency of a Linear Regulator

The efficiency,  $\eta$ , of a linear regulator is defined by the ratio of the delivered output power  $P_{OUT}$  to the power consumption  $P_{IN}$

$$\eta = \frac{P_{OUT}}{P_{IN}} \qquad \begin{array}{l} P_{OUT} = V_{OUT}I_{OUT} \\ P_{IN} = V_{IN}I_{IN} \\ I_{IN} = I_{OUT} + I_{O} \end{array}$$

**Equation 1.1: Linear Regulator Efficiency**

${\bf l}_{\rm Q}$  is the quiescent current of the linear regulator under no-load conditions. The equation can be rewritten:

$$\eta = \frac{(V_{\text{OUT}}I_{\text{OUT}})}{V_{\text{IN}}(I_{\text{OUT}}+I_{\text{Q}})}$$

#### **Equation 1.2: Expanded Linear Regulator Efficiency Equation**

The following example is for a typical 5 volt 3-pin voltage regulator with an input voltage of 10Vdc, output current of 1A and a quiescent current of 5 mA.

The efficiency calculation is then:

$$\eta = \frac{5V \times 1A}{10V \times 1005A} = 0.49$$

Thus, the overall efficiency is 49% and the power dissipation in the converter exceeds the 5W delivered to the load. If the input voltage is lowered to the minimum of 7Vdc, the efficiency rises to 70%, but this is the maximum practical efficiency as about 2V headroom is needed for proper regulation. It is immediately apparent from the efficiency equations that the efficiency of this type of regulator is directly dependent on the input voltage and load and is not constant.

This also means that the voltage regulator has to be equipped with a large enough heat sink to allow safe operation under the worst-case conditions of maximum input voltage and maximum output current.

## 1.1.2 Other Properties of the Linear Regulator

Linear regulators have a number of advantages on the one hand, but also have some disadvantages that require special care in their application and use.

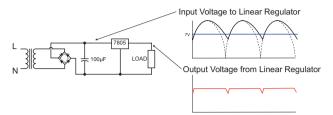

Fig. 1.3: Drop Out Problem with Linear Regulator.

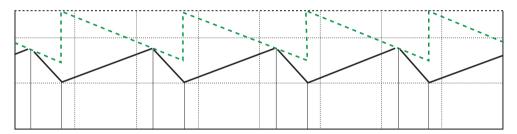

As mentioned before, if the voltage difference between input and output is below the required headroom (typically 2V), then the regulation loop can no longer function properly. A common application problem occurs when a rectified AC input has a high voltage ripple because the smoothing capacitor is too small (Fig. 1.3). If the input voltage drops below the drop out voltage on each half cycle, then the regulated output will show periodic dips at double the mains frequency. These momentary dips will not show up on a multimeter which just measures the average output voltage, but can nevertheless cause "unexplained" circuit problems. This effect can be eliminated by either using larger smoothing capacitors or increasing the turns ratio of the transformer – both rather expensive options.

## 1.1.3 LDO Regulators

The bipolar pass transistor used in the standard linear regulator is used as a current amplifier. The drive current from the output of the error amplifier is multiplied by the small signal current gain of the transistor ( $H_{\text{FE}}$ ) to deliver the load current. The  $H_{\text{FE}}$  of a power transistor is quite low, typically 20-50, so often a Darlington configuration is used with multiple transistors to increase the effective current gain and reduce the output current drawn from the error amplifier. The disadvantage of a Darlington transistor is that the drop-out voltage increases by  $V_{\text{BE}}$  for each stage, so the typical drop out voltage for a standard linear regulator which uses a PNP transistor to drive an NPN Darlington becomes:

$$V_{Dropout} = 2 V_{BE} + V_{CE} \approx 2V \text{ (Room Temp)}$$

At low ambient temperatures HFE decreases, so 2.5 - 3V headroom may be required for reliable regulation over all operating conditions.

Low Drop Out (LDO) linear regulators can operate with a dropout voltage of only a few hundred millivolts by replacing the bipolar transistor with a P-Channel FET. The drop out voltage is then simply the forward voltage across the FET, which is the resistance  $R_{\rm DS}$  multiplied by the load current,  $I_{\rm LOAD}$ . As RDS is typically very low, the drop out voltage is also low.

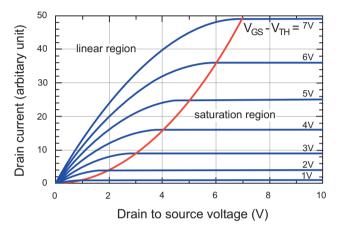

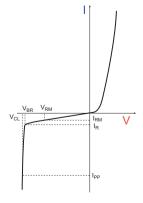

FETs are rarely used in their ohmic region because the gain follows a complex relationship that is both temperature and load dependent (see Fig. 1.4). However, the error amplifier compensates for any drift and non-linearity in the  $V_{GS}$  -  $V_{TH}$  curve because it just compares the output voltage with the reference voltage and adjusts its output accordingly.

The disadvantage of the LDO is that the  $V_{\rm GS}$  -  $V_{\rm TH}$  curve is very steep at high gate drive voltages and very flat at low gate drive voltages, so the error amplifier must have a very low output jitter (heavily damped) and yet be able to quickly react to load or input voltage transients (lightly damped). The result is a necessary compromise between the two operating extremes which can cause problems with either highly inductive or highly capacitive loads.

Fig. 1.4: FET Characteristics

Low Drop Out (LDO) linear regulators can be more susceptible to overvoltage damage and may therefore need more filtering and transient suppression. They also have a more limited input voltage range.

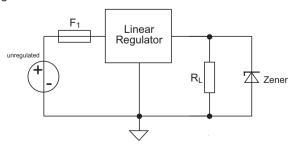

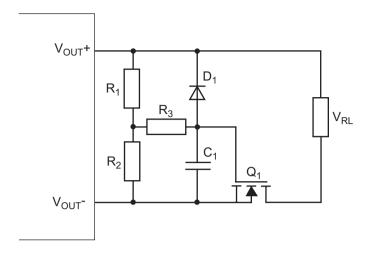

Both standard and LDO linear regulators are also vulnerable to internal failure because the pass transistor is so heavily stressed. If the pass transistor fails, it usually fails short circuit between the collector and emitter. This means that the output is directly connected to the input without any regulation, usually resulting in destruction of the application. Fig. 1.5 shows a possible failsafe protection circuit, using a power Zener clamping diode that will blow the fuse in the event of a regulation fault.

Fig. 1.5: Protection Circuit against Regulator Failure

## 1.2. Switching Regulator

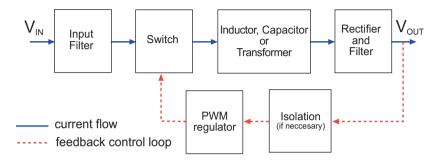

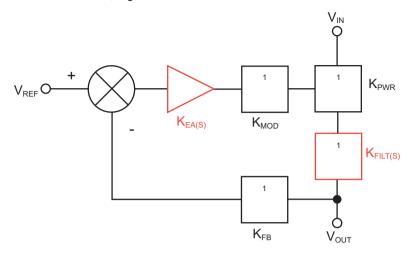

In contrast to linear regulators, which dump excess power as heat in order to limit the output voltage, switching regulators exploit the energy-storing properties of inductive and capacitive components to transfer power in discrete energy packets. The packets of energy are stored either in the magnetic field of an inductor or in the electric field of a capacitor. The switching controller ensures that only the energy actually required by the load is transferred in each packet, so this topology is very efficient. Fig. 1.6 shows the simplified structure of a switching regulator.

Fig. 1.6: Block Diagram of a Switching Regulator

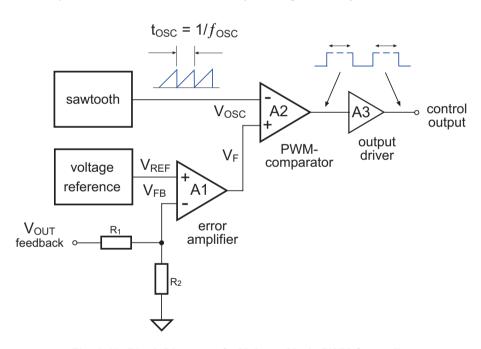

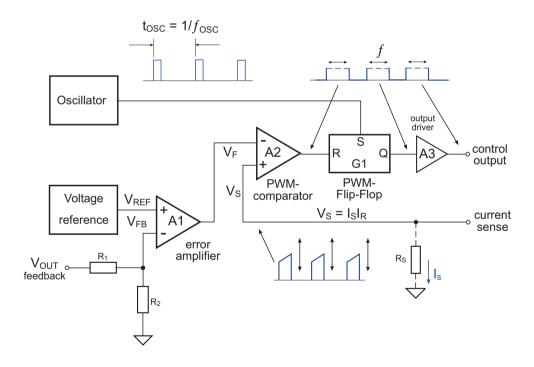

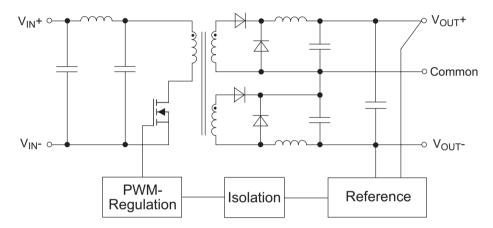

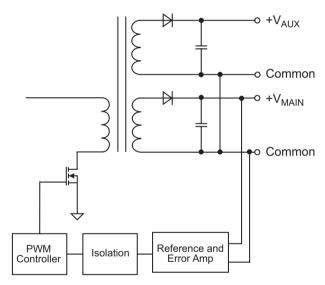

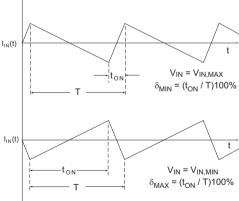

To transfer the energy from input to output in controllable amounts, a more complex regulation technique is needed than that for the linear regulator. The most common type of control is PWM (Pulse Width Modulation), where the amount of energy transferred from input to output is modulated by a variable width pulse with a fixed time interval. The duty ratio of the PWM,  $\delta$ , is the ratio of on-time  $t_{on}$  (the time during which energy is drawn from the source) to the period T (the inverse of the switching frequency  $f_{OSC}$ ).

$$\delta = \frac{t_{\rm ON}}{T}$$

, where  $T = \frac{1}{f_{\rm OSC}}$

**Equation 1.3: Definition of Duty Ratio**

For many switching regulators, the regulated output voltage is directly proportional to the duty cycle of the PWM. The control loop uses the "large-signal" duty cycle to control the power switching element. In contrast, the linear regulator uses the "small-signal" servo loop to limit the current through the pass transistor. PWM control is much more efficient than linear control, because the main losses only occur during each change-of-state of the switch rather than continuously. FETs that are full on or full off dissipate little power.

## 1.2.1 Switching Frequency and Component Size

The size of the storage elements in a switching regulator is roughly inversely proportional to the switching frequency. The stored energy of an inductor is:

$$E(L) = \frac{L I^2}{2}$$

Equation 1.4: Stored Energy in an Inductor

The amount of energy stored in the inductor is proportional to its inductance, but for the same inductive reactance value the inductance is inversely proportional to the frequency. for a fixed amount of energy storage, the value of inductance can be halved if the frequency is doubled, with a corresponding reduction in size.

In capacitive elements of the equation for the stored energy and power are as follows:

$$E(C) = \frac{CV^2}{2}$$

Equation 1.5: Stored energy in a Capacitor

Here again, the capacitor size can be reduced by increasing the frequency without compromising on the total energy storage. Thus doubling the switching frequency halves both the required inductance and required capacitance, leading to a double reduction in the component size. These reductions in physical size are significant for both the manufacturer as well as the customer, because thereby the switching regulators require less packaging and also take up less board space. However, the reduced space requirement goes hand in hand with the increase in RF noise emissions as the switching frequency is increased, so there is an EMC trade-off that limits the highest practical switching frequency to around 500kHz (some very small designs can work at 1MHz or higher, but these need very careful PCB layout and EMC shielding).

## 1.2.2 Switching Regulator Topologies

The term topology refers to the different forms of switching and energy storage element combinations that are possible for the transmission, control and regulation of an output voltage or current from an input voltage source.

The many different topologies for switching regulators can be divided into two main groups:

- a) Non-isolated converters, in which the input source and the output load share a common current path during operation

- b) Isolated converters, in which the energy is transferred via mutually coupled magnetic components (transformers), wherein the coupling between the supply and the load is achieved solely via an electromagnetic field, thereby permitting galvanic isolation between input and output.

#### 1.2.2.1 Non-Isolated DC/DC Converter

The selection from the variety of available topologies is based on such considerations such as cost, performance and control characteristics, which are determined by the application requirements. No topology is better or worse than the other. Each topology has advantages as well as disadvantages and so the choice is a question of the needs of the user and the system application.

For non-isolated DC/DC converters there are five basic transformer-less topologies:

- i. Buck or step-down converter

- ii. Boost or step-up converter

- iii. Buck-boost or step-up-down converter

- iv. Two-stage Inverting Buck-boost (Ćuk converter)

- v. Two stage non-inverting Buck-boost (Sepic converter, ZETA converter)

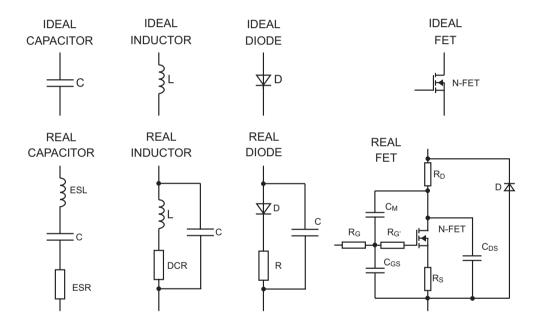

The subsequent explanations assume that the PWM control circuit has a feedback control circuit (not shown) and the correct duty cycle is chosen for the desired output voltage. Also ideal switches (switching transistors or diodes) as well as ideal capacitors and inductors are assumed to better demonstrate the transmission properties of each topology, but before we look at the topologies, a few words about driving switching transistors are opportune.

#### 1.2.2.1.1 Switching Transistors

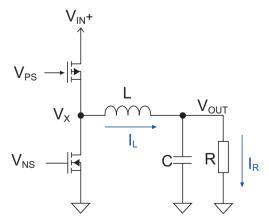

FETs are most commonly used in saturation where the Drain-Source resistance is at the minimum and the power losses in the switch are at a minimum. As long as the gate voltage VGS is well above the threshold voltage  $V_{TH}$ , the FET will be in saturation over the whole load range. (refer to Fig. 1.7).

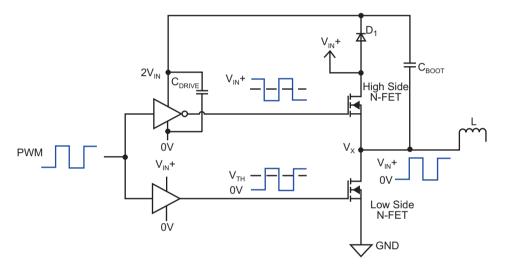

Looking at the simplified synchronous buck converter circuit below, it can be seen that there are two FETs, one switching to GND (low side) and one switching to VIN+ (high side).

Fig. 1.7: Simplified Synchronous Buck Regulator

The low side FET in an N-Channel device that will go into saturation if the drive voltage  $V_{NS} >> V_{TH}$  and switch off if  $V_{NS} < V_{TH}$ .

If the high side FET is a P-Channel device, it will go into saturation if the drive voltage  $V_{PS}$  <<  $(V_{IN} - V_{TH})$  and switch off if  $V_{PS} > (V_{IN} - V_{TH})$ . However, P-Channel FETs have typically  $3 \times 10^{-5}$  the power dissipation of an equivalent sized N-Channel FET and are also more expensive. In many power applications, this is not acceptable and an N-Channel FET as high side driver is preferred, however, this means that the high side driver must be able to generate an output voltage that is higher than the input voltage  $V_{IN}$ .

One commonly used solution for a N-Channel high side driver is to use the square wave signal at  $V_x$  to boost the supply voltage to the high side driver via a bootstrap capacitor and diode  $D_1$ .

Fig. 1.8: Bootstrap circuit for high side driver

The capacitor CBOOT is charged up to  $V_{IN}$ + via  $D_1$  when  $V_X$  = GND and discharges 2 × VIN+ into the high side driver capacitor  $C_{DRIVE}$  when  $V_X$  =  $V_{IN}$ +. Thus the high side driver has a higher voltage supply that can drive the gate of the high side N-FET above the input voltage.

The disadvantage of this simple bootstrap circuit is that at high PWM duty cycles, the bootstrap capacitor does not have enough time to charge up the  $C_{\text{DRIVE}}$  capacitor. Thus operation at close to 100% duty cycle is not possible. This restricts the input voltage and load range of the converter.

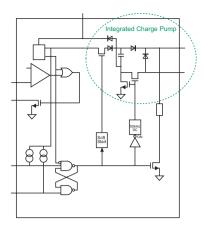

One solution to this problem it to use a separate charge pump oscillator to keep  $C_{DRIVE}$  charged up to above  $V_{IN}$ + over the whole duty cycle range. Such charge pump circuits are often integrated to the controller or high side driver IC (see example below of a MAX1614 high side driver with integrated charge pump).

Fig. 1.9: MAX1614 High Side Driver Block Diagram

#### 1.2.2.1.2 Buck Converter

In the following topolgies, the switching elements are represented as a simple switches. In reality, they can be a transistors, P-FETs or N-FETs, with or without drivers according to the detailed design requirements.

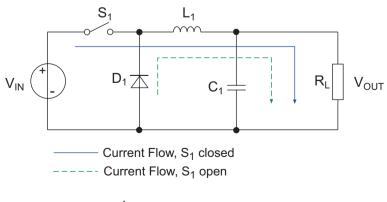

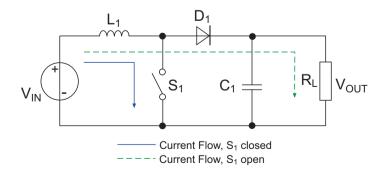

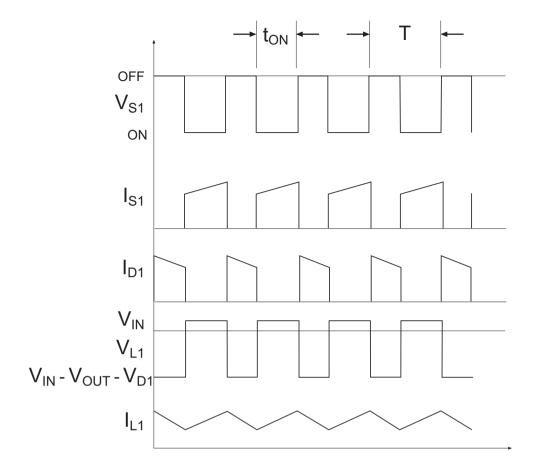

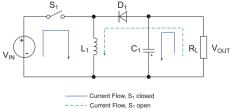

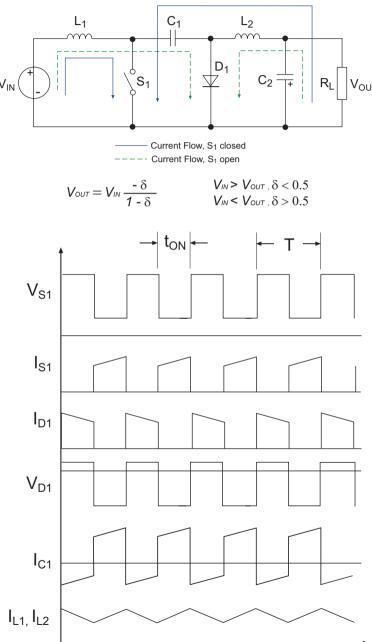

As the name suggests, the step-down or buck converter converts a higher input voltage into a stabilized lower output voltage. A simplified circuit diagram and the main current and voltage waveforms are shown in Fig. 1.10.

The simplest way to understand this circuit is to think of  $L_1$  and  $C_1$  forming a low pass filter. When switch  $S_1$  is closed, the voltage across the load slowly ramps up as the capacitor  $C_1$  charges up through  $L_1$ . If  $S_1$  is then opened, the energy stored in the magnetic field of the inductor is clamped to 0V at the switch end of the inductor by diode  $D_1$ , so the energy has no choice but to discharge into the capacitor and load, causing the voltage across the load to slowly ramp down. The average output voltage is then the mark/space ratio of the PWM control signal multiplied by the input voltage.

$$V_{OUT} = V_{IN} - \frac{t_{ON}}{T} = \delta V_{IN}$$

, valid when  $V_{IN} > V_{OUT}$

Fig. 1.10: Buck Regulator Simplified Schematic and Characteristics

The transfer function can be derived by equating the voltage-time product of the inductance in the ON and OFF conditions. These two products must be the same because of the principle of energy conservation.

For the ON condition: Energy<sub>IN</sub> =  $(V_{IN} - V_{OUT}) t_{ON}$

For the OFF condition: Energy<sub>OUT</sub> =  $V_{OUT}$   $t_{OFF}$ , where  $t_{OFF}$  = T -  $t_{ON}$  and  $\delta$  =  $t_{ON}$  / T

Substituting gives:

$$\begin{aligned} (V_{\text{IN}} - V_{\text{OUT}}) \ t_{\text{ON}} &= V_{\text{OUT}} \ (T - T_{\text{ON}}) \\ V_{\text{IN}} \ t_{\text{ON}} &= V_{\text{OUT}} \ T \\ V_{\text{OUT}} &= V_{\text{IN}} \ (t_{\text{ON}} \ / \ T) \\ V_{\text{OUT}} \ / \ V_{\text{IN}} &= \delta \end{aligned}$$

**Equation 1.6: Transfer Function of Buck Converter**

## 1.2.2.1.3 Buck Converter Applications

The advantages of a buck converter is that the losses are very low - efficiencies of >97% are readily achievable, especially in a synchronous design (see Section 1.2.2.1.8), the output voltage can be set anywhere from VREF to VIN and the difference between VIN and VOUT can be very large. Also, the switching frequency can be several hundreds of kHz to give a very compact construction with small inductors and a fast transient response. Finally, if the switching FET is disabled, the output is zero, so the no-load power consumption becomes negligible. For all of these reasons, the buck regulator makes a very attractive alternative to the linear regulator in many applications.

The RECOM R-78xx series is a pin-compatible alternative to the linear 78xx series. The R-78xx is a complete buck regulator module that does not require any external components for normal operation. It offers 97% efficiency, input voltages up to 72Vdc and quiescent consumption of  $20\mu A$ .

Fig. 1.11: Switching Regulator Buck Converter and Pinout

## Practical Tip

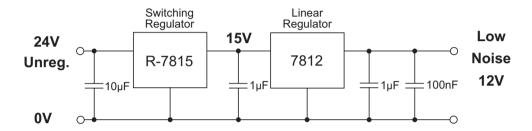

One disadvantage of a buck converter is that the PWM regulator feedback circuit requires a minimum output ripple to regulate properly, as the regulation is typically cycle- by-cycle. The output ripple is also dependent on the duty cycle, being a maximum at 50% duty cycle. So it is not possible to get R/N down to the  $\mu V$  level achieved by linear regulators. If a very clean supply is needed, a buck regulator can be followed by a linear regulator to get the best from both topologies. In the example below, the unregulated 24Vdc is dropped to 15V by a switching regulator with an efficiency of 95%. The linear regulator then provides a clean 12V output with  $<5\mu V$  ripple and noise. The overall system efficiency is around 76%, compared to less than 50% with the linear regulator alone.

Fig. 1.12: Combination of buck regulator and linear regulator

Finally, any switching circuit will generate a pulsed input current which can cause EMI unless adequately filtered (refer to the input current characteristic IS1 in Fig. 1.10). A small 10µF capacitor placed very close to the input pins is thus recommended.

#### 1.2.2.1.4 Boost Converter

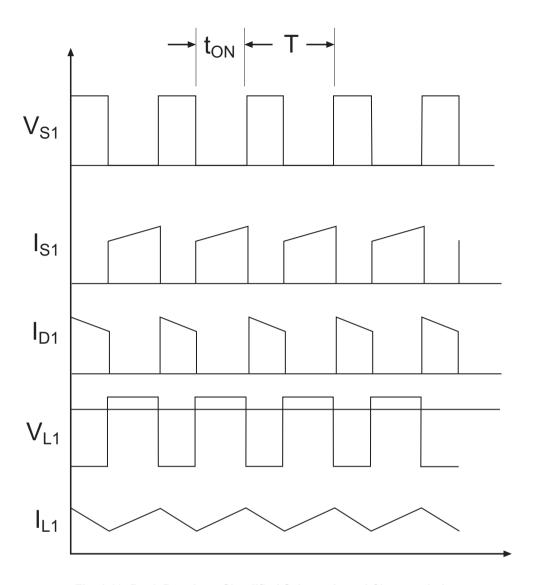

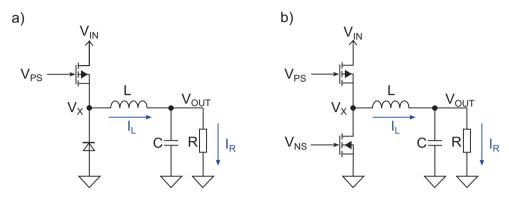

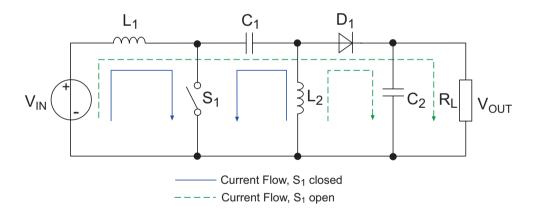

As the name suggests, the step-up or boost converter converts a lower input voltage into a stabilized higher output voltage. A simplified circuit diagram and the main current and voltage waveforms are shown in Fig. 1.13.

$$V_{\text{OUT}} = V_{\text{IN}} \frac{1}{1 - \delta}$$

, valid when  $V_{\text{IN}} < V_{\text{OUT}}$

Fig. 1.13: Boost Converter Simplified Schematic and Characteristics

With  $S_1$  closed, current flows through the inductor  $L_1$  that increases linearly at a ratio  $V_{IN}/L_1$ . During this period the load current is supplied from the stored energy in  $C_1$ . When the switch is opened again, the stored energy in the inductor causes high output voltage superimposed onto the input voltage. The resulting current flows via the freewheeling diode  $D_1$  to supply the load and also recharge  $C_1$ . The current through the inductor falls linearly and proportionally to  $(V_{OUT} - V_{IN})/L_1$ . The derivation of the transfer function is similar to that in the previous section, only the basic equations are rearranged:

For the ON condition: Energy<sub>IN</sub> =  $V_{IN} t_{ON}$

For the OFF condition: Energy<sub>OUT</sub> =  $(V_{OUT} - V_{IN}) t_{OFF}$

$$\frac{V_{OUT}}{V_{IN}} = \frac{1}{1-\delta}$$

**Equation 1.7: Transfer Function of Boost Converter**

## 1.2.2.1.5 Boost Converter Applications

The advantage of the boost converter is that the output voltage can be varied with the mark-space ratio of the PWM signal to be equal to or above VIN. This makes it especially suitable for increasing a low voltage battery output to a more useful higher voltage. However, in practice, a boost ratio of more than ×2 or ×3 makes the feedback stability difficult. Also because the input current pulses increase proportionally to the boost gain, a converter that triples the input voltage draws triple the input current. This pulsed input current can cause EMI and voltage drop issues in the input leads.

One further disadvantage with the boost converter is that the output cannot be switched off without adding a second switch in series with the input as disabling the PWM controller allone does not disconnect the load from the input.

Finally, care must be taken not to allow the input voltage to rise above the output voltage. The PWM controller would then keep  $S_1$  permanently open and the input and output will be connected directly via  $L_1$  and  $D_1$  without regulation. Destructive currents can flow that will quickly destroy both the converter and the load. If this condition cannot be avoided, a topology that permits both buck and boost operation is needed.

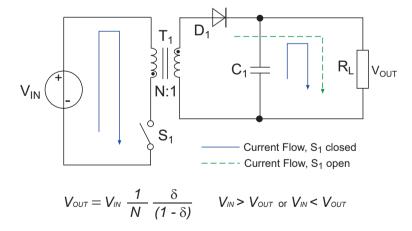

## 1.2.2.1.6 Buck-Boost (Inverting) Converter

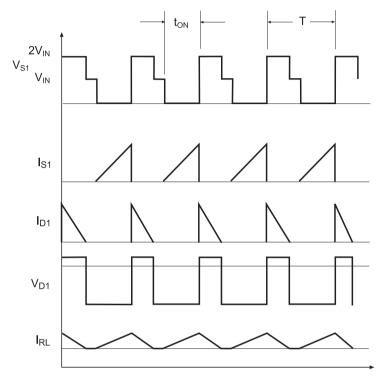

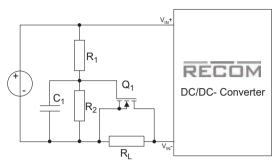

The inverting flyback converter, also called a buck-boost converter, converts an input voltage into a regulated negative output voltage that can be higher or lower than the absolute value of the input voltage. The simplified diagram in Fig. 1.14 shows the basic circuit diagram and associated waveforms.

In this circuit, when  $S_1$  is closed, a current  $IL_1$ , which increases in proportion to  $V_{IN}/L1$  flows through  $L_1$ . Diode  $D_1$  blocks any current flow into the load. During this time, the load current is supplied from the output capacitor  $C_1$ . When switch  $S_1$  is opened, the energy stored in  $L_1$  causes the switch end of the inductor to go negative (the other end of the inductor is grounded). The inverted current now flows into the load consisting of  $C_1$  and  $R_L$  via  $D_1$ . This current decreases in proportion to  $V_{OUT}/L_1$ . Because of the direction of current flow, the output voltage is negative with respect to ground potential. Therefore, this topology is suitable for generating negative voltages only.

$$V_{OUT} = V_{IN} \frac{-\delta}{1-\delta}$$

$V_{IN} > V_{OUT} \text{ or } V_{IN} < V_{OUT}$

Fig. 1.14: Buck/Boost Simplified Schematic and Characteristics

The derivation of the transfer function is similar to that in the previous sections, only the basic equations are:

For the ON condition: Energy<sub>IN</sub> =  $V_{IN} t_{ON}$

For the OFF condition: Energy<sub>OUT</sub> =  $-V_{OUT} t_{OFF} V_{OUT}$

$$\frac{V_{OUT}}{V_{IN}} = \frac{-\delta}{1-\delta}$$

**Equation 1.8: Transfer Function of inverting Buck-Boost Converter**

The advantage of a buck/boost converter is that the input voltage can be higher or lower than the regulated output voltage. For example, this is can be particularly useful in applications that need a stabilised 12V output from a 12V lead acid battery that can have a terminal voltage between 9V when discharged to 14V when fully charged.

Buck/Boosts are also very useful for stabilising photovoltaic cell outputs. A solar cell can deliver very high voltage and current in bright sunlight, but low voltage and current when a cloud passes in front of the sun. As the voltage/current relationship changes, a buck/boost can be used for maximum power point tracking (MPPT) because the input/out- put voltage ratio can be continuously adjusted.

The biggest disadvantage is the inverted output voltage. Again, if used with a battery, then the output voltage inversion becomes irrelevant, because the battery supply can be left floating and the  $-V_{OUT}$  can then be connected to ground to give a positive-going output voltage. Another disadvantage is that the switch  $S_1$  does not have a ground connection. This means that a level translator is needed in the PWM output circuit which can add cost and complexity to the design.

#### 1.2.2.1.7 Buck/Boost Discontinuous and Continuous Mode

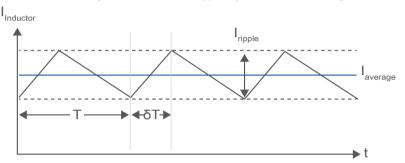

With the step-down or step-up topologies, the energy transferred during each ON pulse is partially determined by the load, so if the load is reduced then the duty cycle is shorte- ned to compensate. With the buck/boost topology, the duty cycle is used to vary the input/output voltage relationship and is not load dependent. So what happens if the load changes?

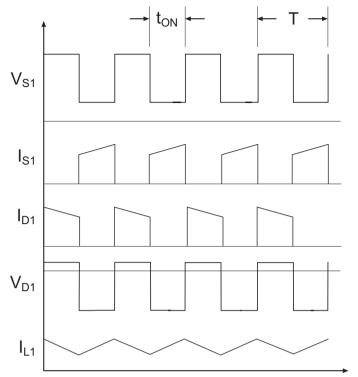

Fig. 1.15: CM and DCM transition

If the load on the converter is high, then the current in the inductor  $I_{L1}$  will be as in Fig. 1.14, a triangle waveform that never falls to zero. The current mode is continuous (CM).

However, if the load on a Buck/Boost converter is very low, then the energy in each ON pulse will be easily sufficient to completely restore the voltage on the output capacitor and the inductor current will then fall to zero for the remainder of the ON pulse period. The inductor current mode is then said to be discontinuous (DCM).

Operation in discontinuous mode adds extra influences to the transfer function as it becomes dependent on the inductor size, input voltage and output current values, so the simple transfer function given in Equation 1.7 becomes more complex:

$$\frac{V_{OUT}}{V_{IN}} = \frac{V_{IN} \delta^2 T}{2 L_1 I_{OUT}}$$

, where  $T = t_{ON} + t_{OFF}$

Equation 1.9: Transfer Function for a Boost Converter in discontinuous mode

The effect of the transition from continuous to discontinuous mode is a change in the input/ output voltage ratio at low loads (Fig. 1.15). Most buck/boost controllers therefore increase their operating frequency at low loads to stay within the boundaries of continuous mode of operation. This maintains the simple transfer function relationship at the cost of more complex EMC filtering to cover a wider range of operating frequencies. Unfortunately, real-life inductors, capacitors and resistors are not ideal, so changing the operating frequency often also adds other errors due to nonlinearities, parasitic effects and unwanted component coupling.

## 1.2.2.1.8 Synchronous and Asynchronous Conversion

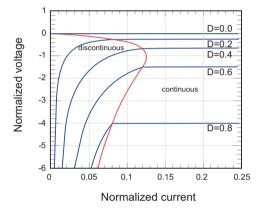

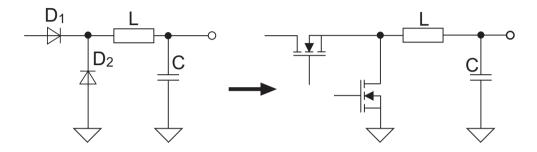

In the topologies presented earlier, a diode is used as the catch rectifier in all of the designs. An alternative would be to replace the diode with a FET that is switched on with an out-of-phase signal to the PWM signal to take over the function of the diode. A circuit using a FET plus a diode is said to be asynchronous and a circuit using two FETs is said to be synchronous. Fig. 1.16 shows the two alternative circuits for a buck converter:

Fig. 1.16: Asynchronous (a) and Synchronous (b) Buck Converter

Replacing the catch diode with a FET has several advantages. The R<sub>DS,ON</sub> of a FET is very low and it does not have the forward voltage drop across it like a diode, so a synchronous design will be more efficient at both high input currents and at low output voltages. The increase in efficiency can be very significant under full load conditions as the catch diode dissipated power can be reduced by as much as a factor of four in a typical medium-power 15W synchronous converter compared to an ansynchronous design. Another advantage is that a high current FET is usually smaller than a power diode, so a space saving on the PCB may be made.

The disadvantage of the synchronous over asynchronous circuit is that the component costs are higher, not only for the additional FET and its driving circuitry, but also for the dead-space timing circuit that stops both FETs being energised at the same time. Another disadvantage is at very low load (<10% Full Load), the synchronous design can actually be less efficient than the asynchronous design. One factor is the additional losses in the low side FET switching circuit which also dissipates power charging and discharging the low-side FET's gate capacitance. Another reason for this is that in an asynchronous design, the inductor current is blocked from flowing backwards by the diode, but in the synchronous design both positive and negative inductor currents can flow. Any negative current represents an additional power loss that the asynchronous circuit does not see.

Controller IC's are readily available that will generate all the signal levels and timing needed for synchronous operation, often including either both the high-side and low-side FETs or just the low-side FET inside the package. Additional timing circuits are often implemented inside the controller IC to increase the efficiency under low-load conditions by pulse-skipping (turning on the FETs less often to reduce switching losses) or by reducing the operating frequency with load. Thus synchronous topologies are more common than asynchronous in most DC/DC converter designs.

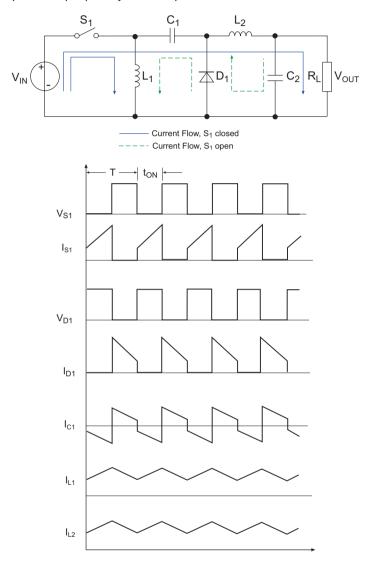

## 1.2.2.1.9 Two Stage Boost/Buck (Ćuk Converter)

The ĆuK (pronounced Chook) boost / buck regulator, also converts an input voltage into a regulated, inverted output voltage higher or lower than the input voltage depending on the duty cycle. The simplified diagram in Fig. 1.17 shows the basic circuit diagram and associated waveforms. It is essentially a boost converter capacitively coupled to an inverted buck converter.

Fig. 1.17: Ćuk Converter Simplified Schematic and Characteristics

It is immediately obvious compared to the previously presented topologies that this topology requires two inductors, however as the current flow in both inductors are the same, they can share a common core. When switch  $S_1$  is closed a current  $I_{L_1}$  flows through  $L_1$  with a ramp rate of  $V_{IN}/L_1$ . Simultaneously, the positive terminal of  $C_1$  is grounded which causes  $C_1$  to discharge a negative voltage via  $L_2$  to recharge  $C_2$  and supply the load  $R_L$  with an inverted current. The current flows through  $L_2$  with a ramp rate of  $(V_{C1} + V_{OUT})/L_2$ . When S1 is opened, the energy stored in  $L_1$  boosts the inductor voltage which is then used to recharge C1 via D1. The current through the inductor  $L_1$  falls with the decay rate of  $(V_{C1} - V_{IN})/L1$ . Simultaneously, the capacitor  $C_2$  discharges through  $L_2$  and diode  $D_1$ , which creates a decreasing  $L_2$  current with the decay rate  $V_{OUT}/L_2$ . The capacitor  $C_1$  is here plays a special role because it is responsible for the entire energy flow from input to output. The value of  $C_1$  is chosen so that the voltage in the steady state is necessarily constant.

Because of the direction of current flow, the output voltage is negative with respect to ground potential. Therefore, this topology is suitable for generating negative voltages only. For the consideration of the transfer function for this topology, the influence of both inductors has to be considered.

#### For L1, the applicable equations are:

For the ON condition: Energy<sub>IN</sub>  $(L_1) = V_{IN} t_{ON}$

For the OFF condition: Energy<sub>OUT</sub>  $(L_1) = (V_{C1} - V_{IN}) t_{OFF}$

#### For L2, the applicable equations are:

For the ON condition: Energy<sub>IN</sub>  $(L_2) = (V_{C1} + V_{OUT}) t_{ON}$ For the OFF condition: Energy<sub>QLIT</sub>  $(L_2) = -V_{QLIT} t_{OFF}$

Substituting gives two equations for the C1 capacitor voltage:

$$V_{C1} = V_{IN} \frac{1}{1 - \delta}$$

and  $V_{C1} = \frac{-V_{OUT}}{\delta}$

Which resolve to give the same result as for the single stage buck/boost converter:

$$\frac{V_{OUT}}{V_{IN}} = \frac{-\delta}{1-\delta}$$

Equation 1.10: Transfer Function of Ćuk Converter

The advantage of the Ćuk converter over the single stage buck/boost converter is that the currents flowing in  $L_1$  and  $L_2$  are the same and continuous. The input and output currents are both effectively LC filtered which makes EMC very simple as very little high frequency interference is generated. And as the currents in both inductors are the same, they can share a common core, which simplifies the construction and helps to reduce ripple currents further.

The design is also very efficient because charging and discharging capacitors via inductors avoids high current spikes with their associative resistive losses. Also, a grounded  $S_1$  switch allows low loss FETs with simple drive circuits to be used.

The biggest disadvantage of the Ćuk converter is the heavy dependence on C<sub>1</sub>. All of the current flowing from input to output must go through this capacitor which must be non-polarised as the voltage across it reverses with each half cycle. The high ripple current generates internal heating which limits the operating temperature. In practice, bulky and expensive polypropylene capacitors must be used. Furthermore, the PWM control loop must be very carefully designed for stable operation. With four reactive components (two inductors and two capacitors), great care must be taken not to create unwanted resonances in the control circuit.

#### 1.2.2.1.10 Two Stage Boost/Buck SEPIC Converter

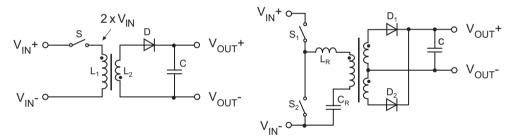

One of the disadvantages of buck/boost converters is the inverted output voltage. This problem can be eliminated by a two stage design called the Single Ended Primary Inductor Converter (SEPIC).

Essentially the design is similar to a Ćuk (two stages: boost converter followed by a buck converter) except in a SEPIC topology, the inductor  $L_2$  and diode  $D_1$  are swapped around. This allows the output polarity to be the same as the input polarity.

Fig.1.18: SEPIC Topology Simplified Schematic

The energy transfer is similar as in the Cuk converter, so gives a transfer function as follows:

$$\frac{V_{\text{OUT}}}{V_{\text{IN}}} = \frac{\delta}{1 - \delta}$$

**Equation 1.11: transfer Function of SEPIC Converter**

Fig. 1.19: SEPIC Converter Characteristics.

The fact that the output voltage polarity is the same as the input voltage makes the SEPIC circuit very useful for battery powered applications using rechargeable cells. The battery charger can then be used both to recharge the battery and to simultaneously power the application because they share the same common ground rail. Like the Ćuk converter, the SEPIC also has a continuous input current waveform which makes EMC filtering simpler.

#### Practical Tip

SEPICs are often used for LED lighting applications because the capacitor  $C_1$  provides inherent output short circuit protection, the feedback loop can be easily modified for constant current instead of constant voltage regulation and a common V- rail makes EMC filtering simpler (LED lighting applications are required to meet strict input harmonic interference limits).

The disadvantages are that the SEPIC converter has a pulsed output current waveform similar to a conventional single stage buck/boost converter and, like the Ćuk converter, has a complex 4-pole feedback function that can easily break into resonance.

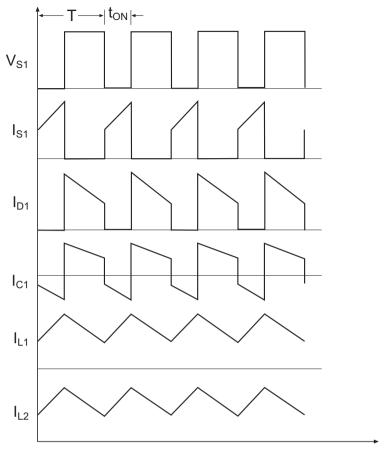

## 1.2.2.1.11 Two Stage Boost/Buck ZETA Converter

Another variation on the SEPIC topology is the ZETA or Inverse SEPIC Converter. Instead of a boost stage followed by a buck regulator, the ZETA converter uses a buck converter followed by a boost stage. The rearranged topology retains the advantage of the SEPIC design in that the output and input polarity are both positive.

Fig. 1.20: ZETA Converter Simplified Schematic and Characteristics

The energy transfer is similar to the SEPIC topology, so gives the same transfer function:

$$\frac{V_{\text{OUT}}}{V_{\text{IN}}} = \frac{\delta}{1 - \delta}$$

**Equation 1.12: Transfer Function of ZETA Converter**

The advantage of a ZETA topology over a SEPIC converter is that the feedback loop is more stable so that it can cope with a wider input voltage range and higher load transients without breaking into resonance. The output ripple is also significantly lower than an equivalent SE-PIC design.

The disadvantage is that a ZETA topology has a higher input ripple current, so it needs a larger C1 capacitor for the same energy transfer (the intermediate voltage is lower) and switch S1 is not grounded, so a level-shifting circuit is needed to drive the P-Channel FET.

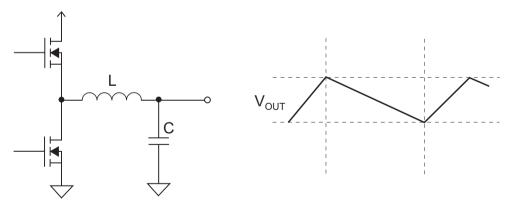

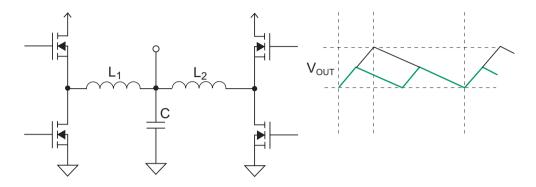

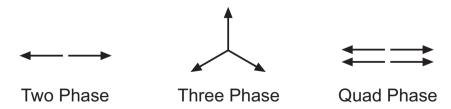

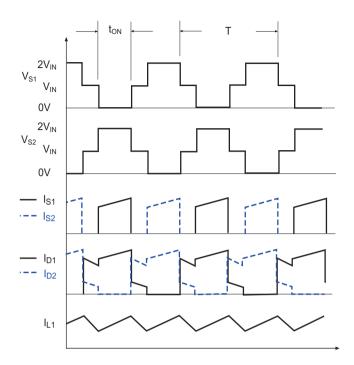

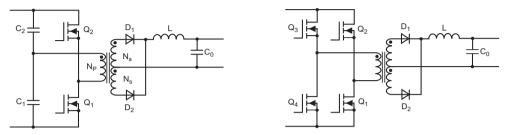

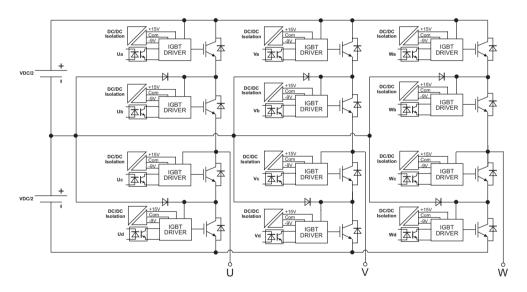

#### 1.2.2.1.12 Multiphase DC/DC Converters

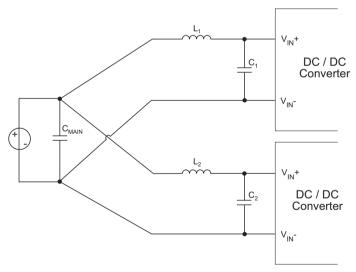

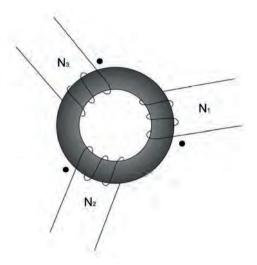

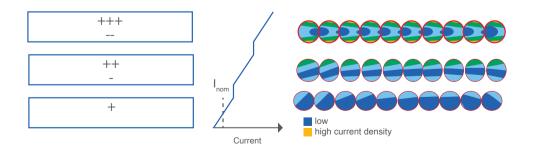

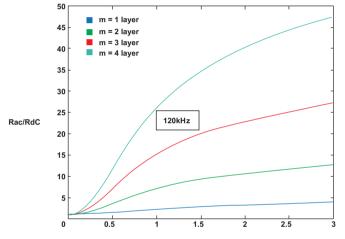

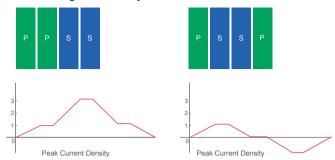

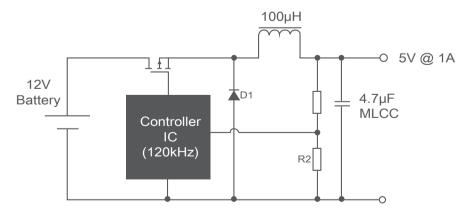

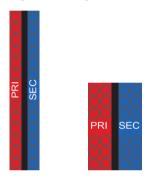

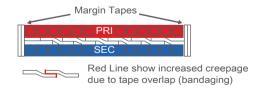

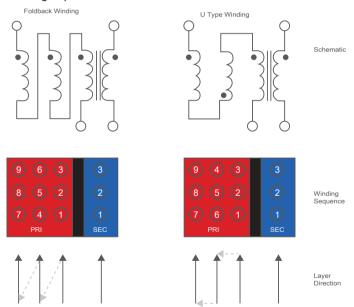

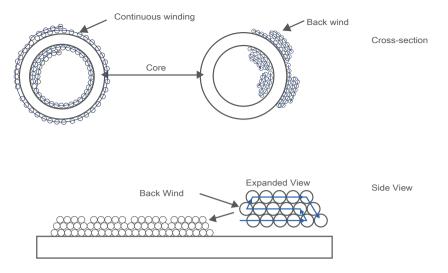

Multiphase DC/DC converters are a good example of the principle of equilibrium in electronics. This means that for any desired benefit, a price must be paid for by some balancing disadvantage. The push for ever faster switching speeds to increase processing power has caused the typical microprocessor core voltage to drop from 5V to 3.3V and then down to below 1V while the increasing gate complexity has led to the demand for ever higher supply currents. Low voltage, high current power supplies are, however, not easy to build.